Designing Sequential Logic Circuits: State Transition Analysis and Counters

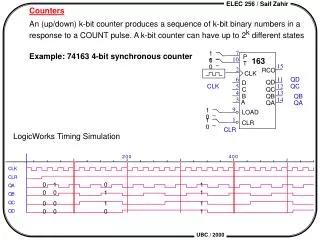

Learn the process of analyzing synchronous sequential logic circuits, including writing driving equations, state equations, output equations, drawing state transition tables and diagrams, and designing counters. Explore methods for designing counters with examples and different functionalities. Understand the cascading of counters for higher-modulus operations and the concepts of asynchronous and synchronous counters.

Designing Sequential Logic Circuits: State Transition Analysis and Counters

E N D

Presentation Transcript

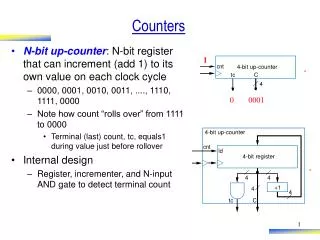

Combinational logic circuit: output only depends on the input. Sequential logic circuit: output not only depends on the input, but also depends on its original state.

The analysis of synchronous sequential logic circuit The process is as follows: 1. Write driving equations of each flip-flop, that is write input logic expressions of each flip-flop. 2. Write state equations of each flip-flop. (substitute driving equations into the characteristic equations) 3. Write output equation according to logic circuit. 4. Drawing state transition table and state transition diagram. 5. Analyze logic function.

Q3 Q2 Q1 Q3* Q2* Q1* Y 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 1 0 0 1 1 0 0 1 1 1 0 0 0 1 0 0 1 0 1 0 1 1 0 1 0 1 0 0 0 0 1 1 0 1 1 1 1 0 0 0 1 State transition table—— method 1

CLK Q3 Q2 Q1 Y 0 0 0 0 0 1 0 0 1 0 2 0 1 0 0 3 0 1 1 0 1 0 0 0 4 1 0 1 5 0 6 1 1 0 1 7 0 0 0 0 0 1 1 1 1 1 0 0 0 0 State transition table——method 2

Two methods to design counter(a) Asynchronous reset(b)Synchronous load

Senary counter Output carry (a) Asynchronous reset

output carry (b)Synchronous load load 0000

Output carry load 1001

74161 Synchronous hexadecimal addition counter

& Q0 Q1 Q2 Q3 1 1 EP C ET CP CP 1 D0 D1 D2 D3 74161 LD RD Design a septenary counter ---------- asynchronous reset

0000 0001 0010 0011 0100 1111 0101 1110 0110 1101 0111 1100 1011 1010 1001 1000

& Q0 Q1 Q2 Q3 1 EP C ET 1 74161 CP CP D0 D1 D2 D3 LD RD Design a septenary counter ---------- synchronous load

0000 0001 0010 0011 0100 1111 0101 1110 0110 1101 0111 1100 1011 1010 1001 1000

Q0 Q1 Q2 Q3 1 EP C ET 1 CP CP D0 D1 D2 D3 1 0 1 0 LD RD Determine the number of the counter Senary counter & 74161

Cascaded counters Counters can be connected in cascade to achieve higher-modulus operation. Cascading means that the last-stage output of one counter drives the input of the next counter.

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q0 Q1 Q2 Q3 Q0 Q1 Q2 Q3 EP C 1 EP C ET 74161(1) 74161(2) ET CP CP D0 D1 D2 D3 1 D0 D1 D2 D3 1 CP RD LD LD RD