Back End FPGA

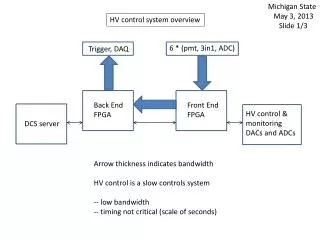

Michigan State May 3, 2013 Slide 1/3. HV control system overview. 6 * (pmt, 3in1, ADC). Trigger, DAQ. Back End FPGA. Front End FPGA. HV control & monitoring DACs and ADCs. DCS server. Arrow thickness indicates bandwidth HV control is a slow controls system

Back End FPGA

E N D

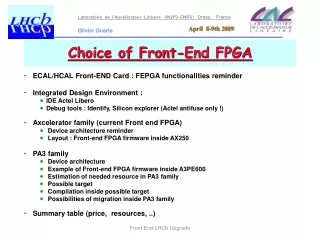

Presentation Transcript

Michigan State May 3, 2013 Slide 1/3 HV control system overview 6 * (pmt, 3in1, ADC) Trigger, DAQ Back End FPGA Front End FPGA HV control & monitoring DACs and ADCs DCS server Arrow thickness indicates bandwidth HV control is a slow controls system -- low bandwidth -- timing not critical (scale of seconds)

Slide 2/3 HV control system: connectivity of front end and back end FPGAs Back End FPGA Front End FPGA GBT Q-SFP? Dual port RAM Dual port RAM SPI engine ADC ADC DAC DAC

Slide 3/3 HV control system: dual port RAM inside both FPGAs USA15 back end Dual port RAM TileCal front end Dual port RAM SPI_Data_1 SPI_Data_2 SPI_Data_3 … SPI control SPI status SPI_Data_1 SPI_Data_2 SPI_Data_3 … SPI control SPI status Dual port RAM is updated through fiber optic links SPI engine ADC ADC DAC The HV slow control process is low bandwidth and not timing-critical. One simple communication method is to uncouple the SPI engine and the updates of the dual-port RAM registers: (1) Dual port memories are mirrored through the fiber optic links. (2) Coordination could be performed through simple handshaking (signals such as Write_SPIand SPI_Busy) (3) SPI engine could be a relatively independent system inside FPGA (SPI engine essentially reduces to a remote-control shift register) DAC