CMS Tracker FED Back End FPGA

120 likes | 132 Vues

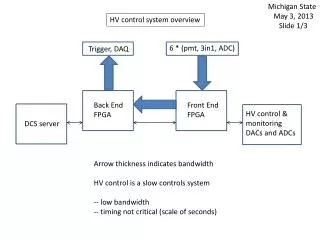

This system provides control and monitoring capabilities for the CMS Tracker FED Back End FPGA. It includes features such as frame synchronization, readout synchronization, data streaming, temperature and voltage monitoring, and interface with VME.

CMS Tracker FED Back End FPGA

E N D

Presentation Transcript

CMS Tracker FED Back End FPGA Frame_Sync_out0 Clock40 Frame_Sync_In0 Readout_Sync_out0 Reset Readout_Sync_In0 TTCrx Monitor_out0 12 FE0 Monitor_In0 VME Internal ~64K Config_In0 TTS Config_out0 J0 7 pairs 4 Data_stream0 Single ended DCI LVDS pair option Frame_Sync_out7 SLINK64 64 Frame_Sync_In7 SLINK J2 32 + 13 pairs Readout_Sync_out7 12 Readout_Sync_In7 ADDR/CNTRL FE7 Monitor_Sync_out7 DATA IN 18 QDR SSRAM x2 QDR Common Address Monitor_Sync_In7 18 DATA OUT Data_stream7 4 Bank DCI Resistors 8 Clock40 LVDS 2 Temp Flags Full flags 3 ef, pf & ff ‘I2C’ LM82 Temp Sense diode Bank Voltages BSCAN Core Voltage

CMS Tracker FED Back End FPGA Clock40 in 1 Channel Link x1 DCMs x2 3 8 Clock40 out x4 Control 3 16 SLINK/Channel Link ‘VME’ In 16 Out Header 8 DDR 64 8 640 MHz LVDS Control Data 8x Lengths, Pointers 8x 1 Fill/run/freeze Reset x8 FF, PF, busy Frame_Syncs x8 Readout_Syncs DECODE CONTROL & MONITOR x8 Load_monitor 18 x8 Data Out Spare 320 MHz 2 FF/PF Flags QDR SSRAM x2/x4 burst 40 Mhz R/W Address Generator 9 TTC Rx 20 Reset Address TTS 80/160 MHz Control Data 4 Data_stream 0 64 18 Data In DDR 4 320 MHz 80 MHz Data_stream 7 160 MHz

Back End Control Block Address VME Interface VME Data Header Control Control FS in 0..7 Frame Sync Interface FS out 0..7 RS in 0..7 Readout Sync Interface Address Generator Data RS out 0..7 Load 0..7 Load/Monitor Interface Monitor 0..7 Header Generation Data tap 0..X Header Data SLINK-VME SLINK Data 0..63 TTC Interface TTC 0..9 Event Scalers FE FPGA FF/PF 0..1 Flow Control Interface TTS 0..X Address Generator Control SLINK CTRL 0..X Reset

Frame Sync Serial Detect Compare CTRL BUS fs_strobe, status= good, some header errors, arrival time error, fatal error FS in 0..7 reset, freeze FIFO 1K HEADER BUS fs_fifo_empty, fs_fifo_full, fifo_data=median header+status 8x Serial Data, markers & control data DPM 1K circular buffer VME BUS

Readout Sync Serial Detect CTRL BUS rs_strobe, status= good, arrival time error, fatal error RS in 0..7 reset, freeze,readout_next RS out 0..7 FIFO 1K Address Gen Total_length_fifo_empty, total_length_fifo_full, fifo_data= total length FIFO 8K fifo_data= 8x sub_lengths FIFO 8K fifo_data= 8x pointer_offsets FIFO 8K HEADER BUS copy_fifo_empty, copy_fifo_full, fifo_data= sub_lengths 8x Serial Data, markers & control data DPM 1K circular buffer VME BUS

Load/Monitor Serial I/O Engine DPM 1K Config in 0..7 Config out 0..7 Output ‘VME’ BUS DPM 1K Input Serial I/O Engine DPM 1K Monitor in 0..7 Monitor out 0..7 Output ‘VME’ BUS DPM 1K Input

SLINK-VME VME-SLINK Readout CTRL BUS QDR/SLINK Interface DPM 1K ‘VME’ BUS FIFO 1K QDR Event Data moved in blocks into DPM Burst transfer over VME Wait on software handshake before continuing Double buffered

TTC Interface TTC Interface CTRL BUS ttc_strobe TTC 0..9 reset, freeze Bx,Ex FIFO 1K Header Em Hdr FIFO 1K DPM 1K VME

Flow Control core VME soft reset Addr Gen FIFO FF Internal FIFO FF Internal Freeze Latch FE FPGA FF Addr Gen FIFO PF Internal FIFO PF TTS BUSY FE FPGA PF Addr GEN FF Addr GEN Controls Fill Flow Control Internal FIFO EF RS Controls Internal Freeze Fill event SLINK CTRL Busy Simplest flow control; Halt on any buffer full Busy on any buffer partially full Empty Flow Control Addr GEN EF Addr GEN Busy Readout event Internal Freeze Diagnostic Event Logger Circular Buffers VME Time stamped Control Registers

CMS Tracker FEDSystem Timing Frame Sync In 256+12 #2234 Header Data ADC Output Frame Sync Median header+ Status Message Frame Sync Out Accept/abort Handshake Message Frame Sync In #2233 Length Readout Sync Out Processed Message #2220 Next/delete #2221 Readout Message Readout Message Readout Sync In #2219 #2220 #2221 Data Burst Data Burst Data Burst Data NB Frame Sync In - Abort/Accept not used, auto accepts. Readout Sync In - delete not used.

CMS Tracker FED Back End FPGA #FFFFF Event N+1 Event N+1 Event N+1 Write Ptr 7 FE 7 Write Ptr 7 Write Ptr 7 Write Ptr 2 Event N Write Ptr 2 Write Ptr 2 Write Ptr 1 FE 1 Write Ptr 0 Write Ptr 1 Write Ptr 1 FE 0 Header Ptr Write Ptr 0 Write Ptr 0 Read Ptr Event N-1 Event N-1 Event N-1 Read Ptr Read Ptr #00000 T0 T1 T2

CMS Tracker FED - Back End FPGA Floorplan Die Package VME FE_FPGA_Inputs SLINK QDR Same frame 456 & 676 ? XC2V1000FG456 - 324 I/O Clocks XC2V1500FG676 - 396 I/O XC2V2000FG676 - 456 I/O XC2V3000FG676 - 484 I/O