Sequential Statements

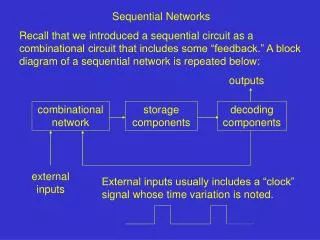

Sequential Statements. Osman Hasan COEN 313. Outline. VHDL process Sequential signal assignment statement Variable assignment statement If statement. VHDL Process. Group of Instructions that are executed sequentially Syntax process declarations; begin sequential statement;

Sequential Statements

E N D

Presentation Transcript

Sequential Statements Osman Hasan COEN 313

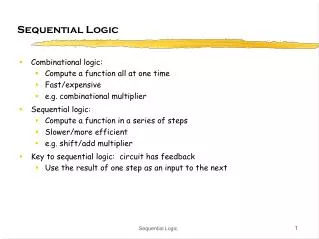

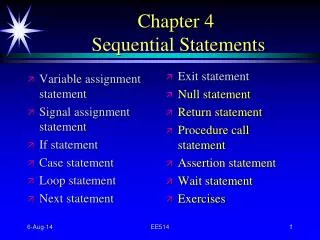

Outline • VHDL process • Sequential signal assignment statement • Variable assignment statement • If statement

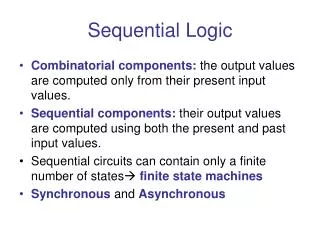

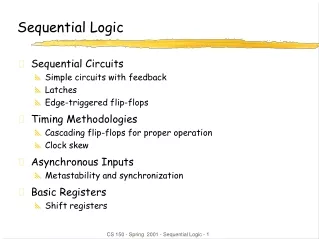

VHDL Process Group of Instructions that are executed sequentially Syntax process declarations; begin sequential statement; sequential statement; . . . end process; The whole process is a concurrent statement 3

VHDL Process - Types With Sensitivity list Process (sensitivity list) declarations; begin sequential statement; sequential statement; . . . end process; A process is activated when a signal in the sensitivity list changes its value • Example: 3 input AND gate • signal a,b,c,y: std_logic; • process(a,b,c) • begin • y <= a and b and c; • endprocess; • What happens if a is removed from the • sensitivity list? 4

VHDL Process - Types With Wait statement Process declarations; begin sequential statement; sequential statement; wait on signals . . . end process; No sensitivity list Process continues the execution until a wait statement is reached and then suspended • Example: 3 input AND gate • process • begin • y <= a and b and c; • waiton a, b, c; • endprocess; 5

Points to Remember A process may or may not be mapped to physical hardware For a combinational circuit, all inputs should be included in the sensitivity list Process with sensitivity list is preferred for synthesis 6

Sequential signal assignment statement Identical to the simple concurrent signal assignment Syntax : signal_name <= value_expression; Inside a process, a signal can be assigned multiple times, but only the last assignment takes effect • Example: • process(a,b,c,d) • begin -- yentry := y • y <= a or c; -- yexit := a or c; • y <= a and b; -- yexit := a and b; • y <= c and d; -- yexit := c and d; • endprocess; -- y <= yexit • Example: • process(a,b,c,d) • begin • y <= c and d; • endprocess; 7

Variable assignment statement Like variables in C/C++ Syntax : variable_name := value_expression; Assignment takes effect immediately What happens if := is replaced with <= • Example: • process(a,b,c) • variable tmp: std_logic; • begin • tmp := '0'; • tmp := tmp or a; • tmp := tmp or b; • y <= tmp; • end process; 8

Quiz 1 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY sig_ass IS END ENTITY; ARCHITECTURE beh OF sig_ass IS SIGNAL sum1,sum2 : INTEGER := 0; BEGIN p0: PROCESS BEGIN WAIT FOR 10 ns; sum1 <= sum1 + 1; sum2 <= sum1 + 1; END PROCESS; END beh; 0 0 0 10 0 0 10 + 1 Δ 1 1 20 1 1 20 + 1 Δ 2 2 30 2 2 30 + 1 Δ 3 3 9

Quiz 2 ENTITY and_or IS PORT ( a,b,c,d : IN STD_LOGIC; output : OUT STD_ULOGIC); END ENTITY; ARCHITECTURE beh OF and_or IS SIGNAL x,y : STD_LOGIC; BEGIN my_process : PROCESS (a,b,c,d) BEGIN x <= a OR b; y <= c OR d; output <= x AND y; END PROCESS; END beh; • Signals are updated at the end of a • process. • If a process is reading the value of • signal, it will read the old • (non-updated) value! • How to Solve this Bug! 10

Outline VHDL process Sequential signal assignment statement Variable assignment statement If statement 11

If Statement Sequential Conditional Statement in VHDL Syntax ifboolean_expr_1 then sequential_statements; elsifboolean_expr_2 then sequential_statements; elsif boolean_expr_3then sequential_statements; . . . else sequential_statements; endif; 12

Example: 4-to-4 Priority Encoder • 4-to-2 priority encoder 15

Last Quiz LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ARCHITECTURE beh OF mystery IS BEGIN p0: PROCESS (data_in1, select_in) BEGIN IF select_in = '0' THEN output <= data_in1; ELSE output <= data_in2; END IF; END PROCESS; END beh; 16