Logic level sequential blocks

This lecture explores the fundamental functional sequential blocks in digital logic, focusing on latches and flip-flops. Students will learn about elementary devices used for single-bit storage, including their behavior, structure, and differences between latches and flip-flops. Key concepts covered include Mealy and Moore machine functionalities, characteristic tables, and the role of set-reset latches in synchronous sequential circuits. Further readings include texts by M. Morris Mano and J. P. Hayes for those seeking to deepen their understanding of digital logic design.

Logic level sequential blocks

E N D

Presentation Transcript

Lecture 5.2 Paolo PRINETTO Politecnico di Torino (Italy)University of Illinois at Chicago, IL (USA) Paolo.Prinetto@polito.it Prinetto@uic.edu www.testgroup.polito.it Logic level sequential blocks

Goal • This lecture presents the set of functional sequential blocks that are usually considered to be “elementary” or “basic” at the logic level.

Prerequisites • Module 3 and 4

Homework • No particular homework is foreseen

Further readings • Students interested in making a reference to a text book on the arguments covered in this lecture can refer, for instance, to: • M. Morris Mano, C.R.Kime: “Logic and Computer Design Fundamentals,” 2nd edition updatedPrentice Hall, Upple Saddle River, NJ (USA), 2001, (chapter 4, pp. 182-201)

Further readings or to: • J. P. Hayes:“Introduction to Digital Logic Design,”Addison Wesley, Reading, MA (USA), 1994, (chapter 6, pp. 390-453)

Outline • Latch • Flip-flop • Scannable Flip-flop

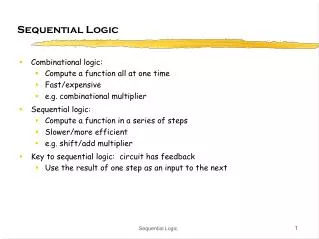

Logic level elementary sequential blocks • Devices capable of storing a single bit: • latch • flip-flop system RT logic device behavior structure physical

Latch vs. Flip-flop CLK D

Latch vs. Flip-flop CLK D Q latch

Latch vs. Flip-flop CLK D Q latch flip-flop Q

Pro’s & Con’s • A latch is a Mealy machine • A flip-flop is a Moore machine • Flip-flops improve testability

Latch • A latch is a single-bit storage device implemented as a Mealy machine. • The most widely used is the so called • D latch.

D latch Q 1D IEEE Symbol C1 QN

D latch Q 1D IEEE Symbol C1 QN CharacteristicTable

D latch Q 1D IEEE Symbol C1 QN CharacteristicTable Describes the logical properties of the latch by describing its operation in tabular form

D latch Q 1D IEEE Symbol C1 QN CharacteristicTable C D Q QN 0 - Q-1 QN-1 1 0 0 1 1 1 1 0 Previous value of Q

C D 1S 1R Q QN 0 - 1 1 Q-1 QN-1 1 0 1 0 0 1 1 1 0 1 1 0 Waveforms C D Q

Hazard-free polarity hold latch • Within the in-house developed LSSD design methodology, IBM uses the following implementation: D C Q QN

Set-Reset latch • The Set-Reset latch can be considered the elementary building block for the implementation of all synchronous sequential circuits. • It has: • 2 inputs S and R • 2 output Q and QN, such that QN = Q’. S Q R QN

Set-Reset latch • Of the 4 combinations of S and R: • One forces Q QN = 0 1 (reset) • One forces Q QN = 1 0 (set) • One lets Q QN unchanged • One is forbidden • The Set-Reset latch can be considered the elementary building block for the implementation of all synchronous sequential circuits. • It has: • 2 inputs S and R • 2 output Q and QN, such that QN = Q’. S Q R QN

Set-Reset latch • Of the 4 combinations of S and R: • One forces Q QN = 0 1 (reset) • One forces Q QN = 1 0 (set) • One lets Q QN unchanged • One is forbidden • The Set-Reset latch can be considered the elementary building block for the implementation of all synchronous sequential circuits. • It has: • 2 inputs S and R • 2 output Q and QN, such that QN = Q’. The correspondenceinput combination performed operationis technology and implementation dependent S Q R QN

Set-Reset latch (nand implementation) S Q R QN S Q R QN Q-1

Karnaugh Map Set-Reset latch (nand implementation) S R Q-1 • 00 01 11 10 • 0 1 1 0 0 • 1 1 1 1 0 Q

Karnaugh Map CharacteristicTable Set-Reset latch (nand implementation) S R S R Q QN 0 0 1 1 0 1 1 0 1 0 0 1 1 1 Q-1 QN-1 Q-1 • 00 01 11 10 • 0 1 1 0 0 • 1 1 1 1 0 Q

Karnaugh Map CharacteristicTable Set-Reset latch (nand implementation) S R S R Q QN 0 0 1 1 0 1 1 0 1 0 0 1 1 1 Q-1 QN-1 Q-1 • 00 01 11 10 • 0 1 1 0 0 • 1 1 1 1 0 • This combination is forbidden due to: • It forces both outputs to 1, thus preventing QN = Q’ • a transition • S R = 00 S R = 11 • forces the circuit to enter an unpredictable state, whose value depends from internal delays.

Karnaugh Map CharacteristicTable Set-Reset latch (nand implementation) S R S R Q QN 0 0 1 1 0 1 1 0 1 0 0 1 1 1 Q-1 QN-1 Q-1 • 00 01 11 10 • 0 1 1 0 0 • 1 1 1 1 0 Q TransitionTable Q-1 Q S R 0 0 1 - 0 1 0 1 1 0 1 0 1 1 - 1

Set-Reset latch (nor implementation) S Q R QN

Karnaugh Map CharacteristicTable Set-Reset latch (nor implementation) S R Q QN 0 0 Q-1 QN-1 0 1 1 0 1 0 0 1 1 1 0 0 S R Q-1 • 00 01 11 10 • 0 0 1 0 0 • 1 1 1 0 0 Q TransitionTable Q-1 Q S R 0 0 - 0 0 1 0 1 1 0 1 0 1 1 0 -

Gated Set-Reset latch • It’s a variation of the Set-Reset latch, in which data are allowed to enter the latch when a given control signal C is asserted, only. 1S Q Symbol IEEE C1 QN 1R

Possible implementation Si 1S Q C1 Ri QN 1R

Excitation table C1 1S 1R Si Ri Q QN 0 - - 1 1 Q-1 QN-1 1 0 0 1 1 Q-1 QN-1 1 0 1 1 0 0 1 1 1 0 0 1 1 0 1 1 1 0 0

Outline • Latch • Flip-flop • Scannable Flip-flop

Logic level elementary sequential blocks • Devices capable of storing a single bit: • latch • flip-flop system RT logic device behavior structure physical

Flip-Flop • A flip-flop is a single-bit storage device implemented as a Moore machine.

Temporal constraints • Flip-flops works properly iff some temporal constraints are satisfied.

Set-up time The time interval in which data inputs and control inputs must be stable before the clock event

Hold time The time interval in which data inputs and control inputs must be stable after the clock event

FF classification w.r.t. data inputs • According to their behavior w.r.t. data inputs, flip-flops are usually classified as: • D • SR • JK • T.

D behavior CLK Q D Q 0 0 1 1 D QN CharacteristicTable

TransitionTable D Q 0 0 1 1 Q-1 Q D 0 0 0 0 1 1 1 0 0 1 1 1 - 0 0 - 1 1 CharacteristicTable

Caveat • Distinction between data inputs and control inputs is context and application dependent.

Example(D = data input) • At any CLK, it stores the input data D Q CLK

Example(D = control input) • If ( D = 0 ) then force Q=0 else force Q=1 D Q CLK

S R Q QN 0 0 1 1 0 1 1 0 1 0 0 1 1 1 Q-1 QN-1 Set-Reset behavior CLK Q S R QN

S R Q QN 0 0 1 1 0 1 1 0 1 0 0 1 1 1 Q-1 QN-1 TransitionTable Q-1 Q S R 0 0 1 - 0 1 0 1 1 0 1 0 1 1 - 1 - 0 1 0 - 1 0 1 CharacteristicTable

JK behavior CLK Q J J K Q 0 0 Q-1 0 1 0 1 0 1 1 1 QN-1 K QN

TransitionTable J K Q 0 0 Q-1 0 1 0 1 0 1 1 1 QN-1 Q-1 Q J K 0 0 0 - 0 1 1 - 1 0 - 1 1 1 - 0 - 0 0 1 - 1 1 0 CharacteristicTable

D FF implemented by a JK FF CLK Q D J K QN