University of Sheffield Electronics Workshop Update Dec. 2010

Detailed overview of testing, design, and progress on various electronic components for target controllers, test boards, daughter-boards, BPS monitoring, power supply, schedule, and upcoming phases.

University of Sheffield Electronics Workshop Update Dec. 2010

E N D

Presentation Transcript

Electronics Update Mice Target Workshop – Dec 2010 P J Smith James Leaver

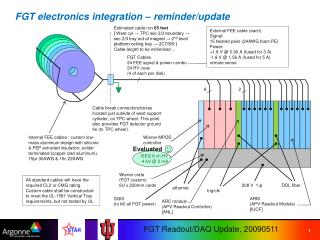

General Overview Phase 1: The target controller in R78 appears to have worked well during the testing. There are a couple of minor issues that need resolving but nothing critical Phase 2 All the Test boards have been completed and they worked as expected including firmware on FPGA. We are currently on the final design for the two daughter-boards that will connect to the FPGA. The Power Supply has been manufactured and is ready for testing – this needs to come back to Sheffield. The schedule seems ok, which is good given the number of distractions... P J Smith - University of Sheffield

Test Boards We built and tested two test boards before designing the final daughter-boards. Test board 1 was a Digital/Analogue converter that tested SPI functionality across two boards. The idea is that this circuit will give an analogue output of the target position. Precision DAC and stable voltage reference to prevent long term drift. • Enabled some familiarity to be gained with designing multilayer PCB’s on a non-critical board. • Tested the VHDL implementation of an SPI interface. The circuit was tested with the serial interface (SPI) running at 8 Mhz – the circuit passed all testing P J Smith - University of Sheffield

Test Boards Test Board 2 was a new version of the optical amplifier circuit used to convert the optical signal coming from the target’s optical block. We built a single channel that has several new digital features that allow much better control over the analogue components. Note that three such channels are required on the final version. Digital features are controlled over an SPI interface with FPGA. The interface was tried and tested on breadboard. As the analogue circuit works at a relatively relatively low frequency we could get away with this. SPI interface tested to 6 MHz. We had some small adapter circuits made from another PCB manufacturer for use on Test Board 2– these were much cheaper. The quality was good and so we have had the Power Supply PCBs manufactured by this company. P J Smith - University of Sheffield

BPS We are going to follow the recommendations of ISIS and monitor the following parameters of every target actuation: • Target Start Position • Target Minimum Position (Apex of target trajectory) • Time to Minimum Position • Time of Actuation This will be done by having an upper and lower limit for each of these parameters loaded into a register in the FPGA. If any one of these parameters exceeds the limits then this will throw an BPS error. Cabling for the BPS signal has been installed into the target rack in the MLCR. Just awaiting our FPGA based signal. P J Smith - University of Sheffield

BPS BNC – BPS1 BNC – BPS2 N.O. Relay contacts on my controller PCB From Mark’s BPS BNC – ISIS CR To ISIS Control Room Monitoring only - Single Line 3 separate firmware signals from FPGA switch 3 relays. Closed Contacts = Signal Good Open Contacts = BPS Error P J Smith - University of Sheffield

Power Supply Power Supply PCB’s designed and manufactured. First board has been stuffed and will shortly be returned to Sheffield for testing. (Large copper area was problematic for small irons at Sheffield) The boards have a small amount of damage on two corners – customs/bad packaging? But doesn’t look like it has got through to the copper layers so these boards should be fine. P J Smith - University of Sheffield

Daughter-Boards The idea behind the daughter boards is to move the circuitry that is currently on veroboard onto pcb’s. Once card will contain most of the analogue circuitry (DC1) and the other card will contain most of the digital circuitry (DC2) At the same time we shall add some additional functionality. We’re also changeing the IC’s where necessary for logical compatibility with 3V3 that the FPGA uses. The design for both cards is now complete and in both cases we are routing the pcb’s Daughter Card 1 Daughter Card 2 P J Smith - University of Sheffield

Example - DC2 6 layer board – routing approximately 30% complete. Note that there is still al large number of components to be added to the board P J Smith - University of Sheffield

Schedule I’ve added a new line on the bottom for making two identical controllers at stage 2 – 1 month addition but shouldn’t delay current schedule. Given that we are loosing James will there be a transitional period of learning the software? P J Smith - University of Sheffield

Phase 3 I’m starting to think tentatively about Phase 3... We would like Ed to design the new DAQ for phase 3 under my supervision. Ed is currently becoming familiar with FPGAs/VHDL. This will present a good opportunity to transfer some knowledge on the functioning of the target. This should free me up to start looking at improving the control algorithms – necessary for increasing the acceleration/reducing bearing wear. P J Smith - University of Sheffield