SC2000/5 CPU and Subsystems

SC2000/5 CPU and Subsystems. Bob Mathews DTV Source Applications Broadband Entertainment Division July 2001. CPU and Subsystems. EZ4102 core Complete details in TinyRISC EZ4102 Tech. Manual (doc.no. DB14-000080-01) EJTAG Debug Tools E-Bus - External System Bus SDRAM-B controller

SC2000/5 CPU and Subsystems

E N D

Presentation Transcript

SC2000/5 CPU and Subsystems Bob Mathews DTV Source Applications Broadband Entertainment Division July 2001

CPU and Subsystems • EZ4102 core • Complete details in TinyRISC EZ4102 Tech. Manual (doc.no. DB14-000080-01) • EJTAG Debug Tools • E-Bus - External System Bus • SDRAM-B controller • BBus DMA Controller (SC2005)

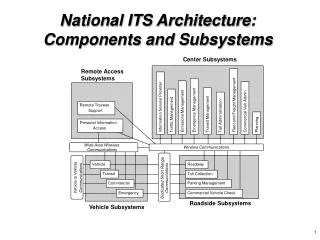

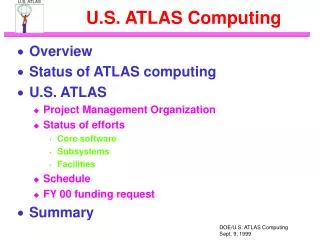

CPU/OSG/XPT/Periph SDRAM I/F A/V SDRAM I/F Audio/Video Decoder TinyRISC CPU (L64105 core) Transport Demultiplexer and DVB Descrambler Video Mixer and Encoder 2 GP Peripheral DMA On-Screen Graphics IEEE 1284 Smart Card 1 Smart Card 0 Modem I/F Tele Text Infrared UART 1 UART 0 I2C GPIO SC2000 Block Diagram E-Bus EZ4102 Debug Port Channel 27 MHz Clock I-Bus S-Bus IEE1284 Smart Cards RS232C Telephone I/R RX I/R TX I2C Front Panel

CPU Subsystem • EZ4102 Core and MDU • BBCC and Cache Controller • MMU Stub and Memory Map • BBus interfaces • Timers • Interrupt controller • EJTAG

CPU Features • 108 MHz TinyRISC EZ4102 Core • 16 Kbytes two-way set associative instruction cache • 8 Kbytes direct mapped data cache • MDU - multiply/divide unit • MMU – translates virtual addresses from the CPU into physical addresses

Instruction Set • Executes MIPS-I, MIPS-II and MIPS 16 instruction sets • Details in mips RISC ARCHITECTURE by Gerry Kane • Approx. 40% code size reduction • 16- and 32-bit code can be mixed • 3 types of Instruction, Immediate, Jump and Register • All instructions execute in 1 cycle except loads, stores and move control

TinyRISC Operation • 3-stage Pipeline, Fetch, Execute, Writeback • 32-bit Memory and Cache interface • Comprises a Register File, Co-Processor, ALU and Shifter • Register file supplies source operands to the execution units • Register files handles the storage of results to the target registers • System Co-Processor processes exceptions including interrupts • ALU performs arithmetic and logical operations • ALU performs address calculations • Shifter operation is self explanatory

Multiply and Divide Unit • 32 x 32 bit signed and unsigned Integer Multiplication • 32 x 32 bit signed and unsigned Integer Multiplication and Accumulation • 5 cycle latency on all Multiplication • 32 bit signed and unsigned Division • 34 cycle latency for Quotient • 35 cycle latency for Remainder • Supports Move From and Move To instructions

BBCC Features • Basic BIU and Cache Controller • Bridge between CPU C-Bus and B-Bus interfaces • Controls access to on-chip caches • Consists of the following modules: • Cache controller • Queue controller • B-Bus controller • System Configuration module

Cache Controller Features • 16 Kbytes two-way set associative I-cache • 8 Kbytes direct mapped D-cache • Programmable block refill sizes for I-cache and D-cache • Instruction Set 0 Line Locking • Software Cache Test Mode

Cache Controller Operation • Controls the Instruction and Data Caches • Identifies Instruction and Data transactions to see if line is in Cache • If line is in Cache then it performs requested transaction • Cache Controller informs the Queue Controller of hit or miss • Cache Controller lets the Bus Controller read and write from and to the Cache and Tag RAMs • The Caches are clocked at 108 MHz

Queue Controller • Orders memory requests to SDRAM-B • Consists of three queues: • Instruction fetch queue • Data fetch queue • Data store queue (32-bit write buffer) • Operation • QC monitors the EZ4102 memory transaction signals and enters requests into appropriate queues • QC arbitrates among requests in the queue and generates requests to the Bus Controller • QC issues Ready signals and stalls the system when necessary

B-Bus Controller • B-Bus is bus interface between CPU and: • S-Bus, E-Bus, I-Bus and ICE Port • 32-bit Address and Data Bus width • 0 to n Wait States • 1, 2, 4 and 8 word Burst transactions • Write burst transactions • Back-to-back transactions • Bus Error and Retry reporting • Multiple Bus Masters possible

MMU Stub • Operates when the MMU soft mapping is disabled. • Hard Maps kseg0 and kseg1 virtual CPU addresses to the lower 512 MB of physical memory Virtual address Physical address 0x8000.0000 - 0x9FFF.FFFF (kseg0) 0x0000.0000 to 0x1FFF.FFFF 0xA000.0000 - 0xBFFF.FFFF (kseg1) 0x0000.0000 to 0x1FFF.FFFF (MMU soft mapping is not used by LSI FTA application code.)

E-Bus Controller • External system bus • connects to external memory and peripherals • discussed in later section

I-Bus Controller • Provides CPU access to internal SC2000 registers including A/V and peripheral function • Software must use non-cache addresses to access this region • I-Bus controller manages acknowledge handshakes and wait states to these registers • No software configuration required

Timers • Four general-purpose timers • Timers 0/1 run at 54 MHz • Timers 4/5 run at 108 MHz • One-shot mode or continuous count down mode • Timer 2 - Watchdog • Resets the CPU if watchdog expires twice and interrupt is not serviced • Timer 3 - Access Surveillance • Monitors accesses from CPU as well as the E-Bus write pipeline • Generates bus error if timer expires before access completes • Interrupt capability provided for all timers

Interrupt Controller • 22 I-Bus Interrupt Lines • Interrupts from all subsystems are grouped onto one bus all_intp[31:0] • Can be routed to any of the six MIPS core interrupt inputs • Level-sensitive interrupts • INTC registers • Interrupt Control - CQBUSINT[5:0] - creates interrupt matrix • Interrupt Status - CQBUSINTS - provides status of I-Bus interrupts • MIPS Cause register - provides status of six MIPS interrupts • MIPS Status register - provides mask capability for six MIPS interrupts • Interrupt priority and handling is software-driven

SC2000 Product Training EJTAG Debug Tools

EJTAG Debug Tools • Agenda • Overview • Features • Benefits • Description

EJTAG Debug Overview • EJTAG is a non-intrusive on-chip debug standard adopted by the MIPS partners. • LSI Logic follows the EJTAG revision 1.5.3 specification for its TinyRISC and MiniRISC CPU cores. • Current EJTAG Debug Solution: • Runs only on PC platforms (Windows 95, 98, NT). • Supported with LSIDBG.EXE (download DIL 2.x) • Works only with Green Hills MULTI 1.8.9 (or later) toolchain. • Does not support PC Trace (i.e. supports only hardware breakpoints). • All features are not available in all probes

EJTAG Debug Environment With EJTAG Connector Macraigor Raven probe and EPI Majic Probes supported. EPI (Embedded Performance In. solution supports both run-time control and PC Trace capture. LSI Logic Milpitas uses Macraigor probe extensively; has no experience with EPI probe.

EJTAG Features • Non-intrusive communication between debug resources and EJTAG probe through standard JTAG interface Test Access Port. • DMA access through EJTAG interface for memory inspection/manipulation and code download. • Processor access through EJTAG interface, eliminating debug code on target. • Dedicated debug exception vector and instructions. • Software Debug Break (SDBBP) • Debug Exception Return (DERET)

EJTAG Features (cont.) • Special CP0 registers for debug exception processing. • Debug Exception Program Counter (DEPC) register • Debug Exception Save (DESAVE) register • Hardware single step - automatic generation of debug exception after each executed instruction. • Break module consisting of: • 2 Instruction Break channels • 2 Data Break channels • 2 Processor Break channels • Real-time program counter trace for monitoring CPU execution.

EJTAG Probe Advantages • EJTAG Probe Advantages over Emulators: • Low pin-count interface needed to connect EJTAG Probe to target system. • No probing effects on target signals. • EJTAG Probe can be re-used for other processor derivatives. • EJTAG interface on target board can also be used for board testing and diagnostics. • EJTAG Probe Advantages over ROM Monitors: • No need for debug monitor on target board. • No serial port required on target system. • Required for code download/flash programming on EVB2005

EasyMACRO Module • Provides basic debug capabilities. • Full EJTAG interface enabling: • Fast code download • DMA access • Processor access via EJTAG probe • Debug exception processing with: • Associated CP0 registers • EJTAG Debug instructions for software breaks • Hardware Single Step

Extended Debug MACRO • Break Module • Provides hardware breaks triggered by instruction and data transactions on virtual and physical addresses as well as data values. • Eliminates inserting SDBBP instructions into application code. • Allows breaks in ROM code. • Real-time Program Counter Trace • Monitor CPU execution (cache or un-cached) in virtual address space.

EJTAG Registers • Occupies address range 0xFF30.0000 to 0xFF3F.FFFF. • Debug Control Register (DCR) • Break Module Registers • Extended CP0 Debug Registers: • Debug register indicates cause of debug exception. • DEPC contains address in user application where execution should resumed after debug exception. • DESAVE is used as temporary storage when saving register file. • Full access is only available in debug mode.

Break Module Overview • Instruction Break Channel • Compares instruction break address with virtual address of instructions fetched from memory or cache. • Data Break Channels • Compares a data break address with virtual address of load/store data transactions from memory, cache, or I/O. • Load/store data can also be compared. • Processor Bus Break Channels • Compares a break address with physical address of all bus transactions, which includes: • Instruction fetches • Data load/store from memory, cache, or I/O. • Data Value can also be compared.

PC Trace Overview • PC Trace outputs the following: • Status codes identifying type of executed instructions (one code per clock cycle). • Virtual address is output serially when sequential program flow is altered by a jump, branch, or an exception. • Output Trace is used by debug host to explore behavior of CPU; • Routines executed • Interrupts serviced

PC Trace Overview (cont.) • The EJTAG probe will record a trace around an event triggered by the Break module. • Allows trace of processor execution even with caches enabled. • On-chip debug logic can detect any changes in program flow. • Code branches are output via EJTAG debug port in real-time and captured in trace memory of EJTAG probe. • Host computer software will re-construct address of all executed instructions by processing raw trace data.

More Information on EJTAG • EJTAG Revision 1.5.3 Specification • Intranets Sites: • MIPS Applications web site • http://eng-www/documents/consumer/applications • MIPS System Software web site • http://saltlake • Source for download of LSI MIPS tools • MIPS Marketing web site • http://planet/products/consumer/mips/mipsmktg

SC2000 Product Training E-Bus - External System Bus

Ebus - external system bus • Agenda for Ebus discussion • Features / Overview • Signals • Mux/demux bus configuration • Ebus address areas • Timing overview • Ebus register descriptions • Boot read • Examples • Ebus programming guide • External bus master mode • ATA interface support (SC2005)

Ebus features • Highly flexible, highly programmable bus interface • Programmable timing for control, address and data • Programmable wait states • Burst mode support (e.g. synchronous flash) • Multiplexed or demultiplexed bus configuration • 64 Mbyte virtual Ebus address space • Automatic scatter/gather operations • Six chip selects - CSn[5:0] • CSn5 can be used as MEMSTBn (via strap option) • Support for external bus master

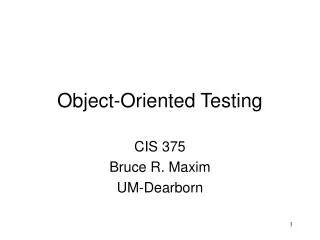

External ICE pins Internal S-Bus SerialICE port S-Bus ctrl External E- Bus E-Bus ctrl C-Bus B-Bus CPU BBCC k I-Bus ctrl n i L Internal x e l MDU I-Bus MMU Stub F Timers I-Cache IRQ-Ctrl D-Cache Statistic System block diagram

Ebus signals - internal bus master • AD[31:0] - multiplexed address/data bus • ADDR[7:0] - fixed address outputs • ALE - address latch enable • BEn[3:0] - byte enables for four byte lanes • CSn[5:0] - chip select outputs • Watch out for default values - see CEPINMODE register • EACKn - acknowledge input • INTn[4:0] - interrupt inputs • MEMSTBn - memory strobe • RDn - read strobe • WRn - write strobe

Mux/demux bus configuration • Mux bus - 32-bit address/data • AD[31:0] signals used • Required for external devices with 32-bit data bus • External address latch required • Demux bus - 24-bit address, 16-bit data • Can be used by 8- and 16-bit peripherals with maximum 24-bit addressing (16 Mbytes per chip select) • No external components required • AEN bit is set, AHLDF field is zero

Ebus addressing • 8-, 16- and 32-bit devices are mapped to specific CPU/Ebus address areas • 32-bit 0x1000.0000 to 0x13FF.FFFF 64 Mbytes • 16-bit 0x1400.0000 to 0x17FF.FFFF 64 Mbytes • 8-bit 0x1800.0000 to 0x1BFF.FFFF 64 Mbytes • Note: Only the lower 24 address bits are physically output in the demux mode • Automatic scatter/gather operations • Scatter used for Ebus writes • Gather used for Ebus reads • BEn[3:0] signals are used to control four byte lanes