Moving Test Applications One Step Closer to RTL

200 likes | 364 Vues

Moving Test Applications One Step Closer to RTL. Zainalabedin Navabi; navabi@cad.ut.ac.ir Nastaran Nemati Electrical and Computer Engineering University of Tehran Tehran, Iran. University of Tehran. Moving Test Applications One Step Closer to RTL. Testing is done at the gate level

Moving Test Applications One Step Closer to RTL

E N D

Presentation Transcript

Moving Test Applications One Step Closer to RTL Zainalabedin Navabi; navabi@cad.ut.ac.ir Nastaran Nemati Electrical and Computer Engineering University of Tehran Tehran, Iran University of Tehran Zainalabedin Navabi, University of Tehran

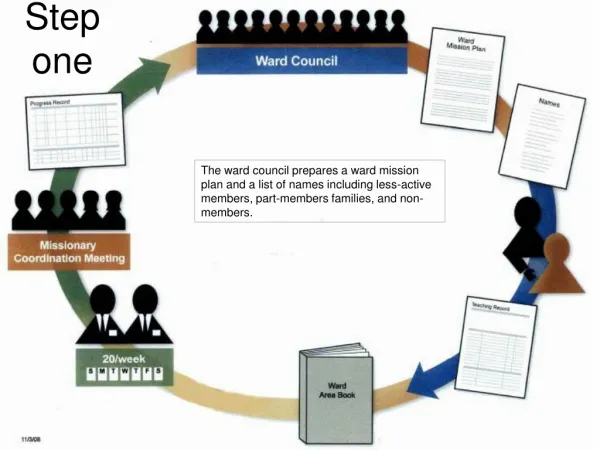

Moving Test Applications One Step Closer to RTL Testing is done at the gate level Design is at the RTL, and moving up Massive amount of HDL based design software Still, test engineers work with gate level tools Need to bring test and design engineers closer Uniform set of tools Motivations Zainalabedin Navabi, University of Tehran

Moving Test Applications One Step Closer to RTL The gap between design and test is widening Zainalabedin Navabi, University of Tehran

Moving Test Applications One Step Closer to RTL For testing, we have not taken advantage from the massive software development and progresses in HDLs For most test applications we start from scratch Verification, design assertions, formal and semi-formal methods are happening Why not take advantage of them? Why not reuse all this HDL based RT level tools Zainalabedin Navabi, University of Tehran

Moving Test Applications One Step Closer to RTL For example: For BIST evaluation we have to develop new software or to add complex patches to our HDL based simulation DFT analysis is the same In test generation every new method requires new data structure, new software programs We are not taking advantage of all this HDL based software Zainalabedin Navabi, University of Tehran

Moving Test Applications One Step Closer to RTL Perhaps we need new methods that can use HDL software Not all necessarily existing test methods can be implemented in HDLs; so we need research in this area. Perhaps new fault simulation and test generation methods Perhaps we should look at sequential test generation which is practically nonexistent; we should revisit sequential TG Zainalabedin Navabi, University of Tehran

Moving Test Applications One Step Closer to RTL Maybe some of old methods will not work well with HDL environments Mixed level of HDLs create new opportunities for some applications Maybe HDL brings new way of doing things Need new methods that can rely on HDL based software programs Zainalabedin Navabi, University of Tehran

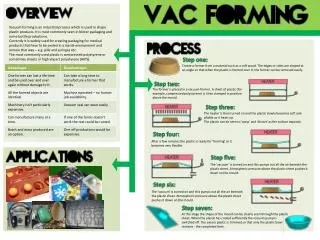

Moving Test Applications One Step Closer to RTL Methods Facilities Mechanisms Zainalabedin Navabi, University of Tehran

Methods to be implemented in HDLs Fault simulation Test generation Scan evaluations BIST evaluation, etc To achieve the above, facilities are needed Manipulation of node values Explore design structure Monitoring node events Lookup node values Mechanism to add such facilities are ‘FOREIGN in VHDL C/C++ interface Use of PLI / VPI Moving Test Applications One Step Closer to RTL Zainalabedin Navabi, University of Tehran

Moving Test Applications One Step Closer to RTL Facilities Sw Tools HDL Utilities Zainalabedin Navabi, University of Tehran

Fault list compilation Fault collapsing Bridging, coupling, transient fault injection Test generation Controllability Observability X-path check Justification Get sequential state Fault simulation Fault injection Fault removal Module enabler / disabler Utilities Zainalabedin Navabi, University of Tehran

DFT and BIST evaluation Fault injection Fault removal Fault simulation utilities Power analysis Utilities Zainalabedin Navabi, University of Tehran

Fault list compilation Applications Zainalabedin Navabi, University of Tehran

Serial fault simulation Applications Zainalabedin Navabi, University of Tehran

DFT evaluation Applications Zainalabedin Navabi, University of Tehran

Mixed Functional / Structural TPG Use OVL assertions Perform HDL based TG Make tests based on firing assertions Evaluate functional tests Filter functional tests Detect remaining faults with HDL based structural methods Test Methods Zainalabedin Navabi, University of Tehran

Test Methods module and_n (out,in); input [(n*nf)-1:0] in; output [nf-1:0]out; reg [nf-1:0]val; integer i; always@(in) begin val = in[nf-1:0]; for(i=1; i<n; i=i+1) begin val=val & in[(nf*i)+:nf]; end end assign out=val; endmodule Parallel Fault Simulation Zainalabedin Navabi, University of Tehran

Test Methods Hierarchical Fault Simulation Zainalabedin Navabi, University of Tehran

Test Methods Sequential Test Generation × 000 01111 5 111 00011 011 11110 001 11100 000 10010 110 01000 100 11111 111 10001 010 01100 011 01111 011 10101 001 00011 3 101 00111 011 11001 010 10001 101 11001 4 111 11100 4 001 01000 5 × × × × × Randon tests × Internal states × × × × Detected faults Selected test vectors × × ×

Developed utilities for unified RT level design and test tool sets Used for closing design and test gap An educational setting for teaching testers and test methods A research platform for developing new algorithms Developing new test tools Summary Zainalabedin Navabi, University of Tehran