MicroTESK : Automation of Test Program Generation for Microprocessors

230 likes | 384 Vues

RAS. ISP. MicroTESK : Automation of Test Program Generation for Microprocessors. Alexander Kamkin kamkin@ispras.ru. Institute for System Programming of the Russian Academy of Sciences (ISPRAS) http://hardware.ispras.ru. RAS. ISP. What does “MicroTESK” stand for?.

MicroTESK : Automation of Test Program Generation for Microprocessors

E N D

Presentation Transcript

RAS ISP MicroTESK: Automation ofTest Program Generation for Microprocessors Alexander Kamkin kamkin@ispras.ru Institute for System Programming of the Russian Academy of Sciences (ISPRAS) http://hardware.ispras.ru

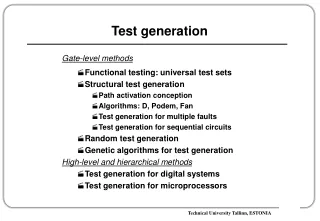

RAS ISP What does “MicroTESK” stand for? • Micro = Microprocessor • Microprocessor = programmable device • Programmable = program-controlled device • TESK = TEsting and Specification ToolKit • Testing = simulation-based verification • Specification = specification-driven approach • Toolkit = computer-aided automation MicroTESK is a specification-driven (model-based) approach that automates simulation-based verification ofprogrammabledevicesbymeansoftestprograms IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Levels of microprocessor verification Unit-level verification Core-level verification Model of a particular unit is tested Model of a microprocessor is tested as a whole via inputs and outputs signals with the help of test programs lui s1, 0xdead ori s1, s1, 0x0 lui s3, 0xbeef ori s3, s3, 0xf add v0, a0, a2 sub t1, t3, t5 add t7, s1, s3 IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

0x2000: lui ... 0x2004: ori ... 0x2008: ori ... 0x200c: lui ... 0x2010: add ... 0x2014: sub ... 0x2018: add ... 0x2000: lui ... 0x2004: ori ... 0x2008: ori ... 0x200c: lui ... 0x2010: add ... 0x2014: sub ... 0x2018: add ... lui s1, 0xdead ori s1, s1, 0x0 lui s3, 0xbeef ori s3, s3, 0xf add v0, a0, a2 sub t1, t3, t5 add t7, s1, s3 RAS ISP Test programs-based verification Target Design (RTL, FPGA) Execution traces (formatted text) Test programs (assembler, C) Trace comparator (Perl, C/C++) Reference simulator (C/C++, ADL) IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

IF ID EX WB lui s1, 0x2779 ori s1, s1, 0x0 lui s3, 0x4ee ori s3, s3, 0xf add v0, a0, a2 sub t1, t3, t5 add t7, s1, s3 IF ID EX WB Random Generation Template-Based Generation Model-Based Generation RAS ISP Approaches to test program construction Unformalized knowledge ? Design Requirements Test programs Manual Development Formalized knowledge IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Advantages of model-based testing • Formalization helps to find problems in a design • Deeper comprehension of requirements • Formal checking of model consistency • Models automate verification of a design • Correctness estimation • Test sequence generation • Testing adequacy criterion • Models simplify tests maintenance • One model, many tests • Reuse of models and testing knowledge IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Approaches to design modeling Cycle-accurate models Instruction-level models ABS.fmt (fd:FPR, fs:FPR) {...} ADD (rd:GPR, rs:GPR, rt:GPR) {...} ADD.fmt (fd:FPR, fs:FPR, ft:FPR) {...} ... XOR (rd:GPR, rs:GPR, rt:GPR) {...} XORI (rd:GPR, rs:GPR, rt:IMM) {...} To generate tests, FSM models are used Test templates are used for verification ADD x, y, z @ z ≥ 0LD u, x, z @ Cache_HitDIV y, u, x @ Division_By_Zero ... DIV.S f, g, h @ Hard_To_RoundADD.S i, f, h @ Inexact MUL.S g, i, f @ Invalid IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Combinatorial test program generation • Tests are constructed by combining • Sequences of instructions • Test situations for instructions • Dependencies between instructions • Execution traces, if branches are used • Volume of tests is reduced by heuristics • Equivalence of instructions • Length of sequences • Depth of dependencies • Length of execution traces IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

move b, 0x4 move t, 0 store t, (b) move c, 1 load a, (b) add c, a, d move f, 0x4 load e, (f) move t, 2 store t, (f) move g, 0xd bne c, g, error ... ISP RAS Structure of test programs … initialization test situation test case test action register dependency address dependency test oracle … IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Instruction specification instruction ADD(rd, rs, rt) • Instruction interface • Instruction operands • Instruction precondition • Execution function • Calculates outputs • Updates a model state • Assembler format • Textual representation output rd: GPR, Word input rs: GPR, Word input rt: GPR, Word if NotWordValue(GPR[rs]) or NotWordValue(GPR[rt]) then UNPREDICTABLE endif temp (GPR[rs]31||GPR[rs]31..0) + (GPR[rt]31||GPR[rt]31..0) if temp32temp31then SignalException(IntegerOverflow) else GPR[rd] sign_extend(temp31..0) endif ADDrd, rs, rt IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

0x1 0x0af1036f 0x0 tag 0xd 0x3 0xffff0a31 0xf47298b9 data 0xdeadbeef ... ... ... 0x0000 0x003e 0x003f 0x0001 0xb000 0xa010 0xb020 0xa000 ... VPN PFN 0xa 0x19d02c34 0x2 0x7420ba9c Cache (L1/L2) TLB ISP RAS Test situations and dependencies if NotWordValue(GPR[rs]) or NotWordValue(GPR[rt]) then UNPREDICTABLE endif temp (GPR[rs]31||GPR[rs]31..0) + (GPR[rt]31||GPR[rt]31..0) if temp32temp31then SignalException(IntegerOverflow) else GPR[rd] sign_extend(temp31..0) endif • Parameters • Specifies family of test situations / dependencies • Constructor / constraint • Constructs / constrains values of the operands • Preparator • Creates initialization program of the instruction IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

move b, 0x4 move t, 0 store t, (b) add ... ... ... move c, 1 sub load ?, (?) load a, (b) move f, 0x4 load lui s1, 0xdead ori s1, s1, 0x0 lui s3, 0xbeef ori s3, s3, 0xf add v0, a0, a2 sub t1, t3, t5 add t7, s1, s3 add c, a, d add ?, ?, ? store move t, 2 load ?, (?) load e, (f) store t, (b) ISP RAS Test program generation scheme Testprogram normal overflow cache hit cache miss register dependency address dependency cache miss normal generation parameters cache hit address dependency register dependency IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP MicroTESK tool support • The approach is supported by the MicroTESK test program generator • Test programs are generated according to the specified goals • Technology and tool provide high level of automation • Test programs might include checks of microprocessor state • Specifications are developed in Java language • There are ready-to-use test data generators • Generator has graphical user interface IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Generator development process IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP How a MicroTESK generator looks like IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Case studies • Memory subsystem • MIPS64 microprocessor • DSP co-processor • Floating-point co-processors • DMA controller • Branch prediction unit IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Some statistics Many critical bugs were found in the designs, which had been verified by hand-written, random-generated, and template-based test programs IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Future directions • Automatic extraction of test coverage • Advanced test template generation • Integration with ADL (ISE, nML, LISA, etc.) IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Extraction of test situations TLB Hit, Valid Hit, Invalid Miss Exception: TLBInvalid Exception: TLBRefill L1 Hit Miss Normal1 Normal2 IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Extraction of dependencies associative buffer TLB<TLB_ENTRY, 64> { VIRTUAL_PAGE_NUMBER tag( VIRTUAL_ADDRESS va) { ... } ... INTEGER index(VIRTUAL_ADDRESS va) { ... } ... } structureTLB_ENTRY { VIRTUAL_PAGE_NUMBER vpn; PHYSICAL_PAGE_NUMBER pfn; ... } IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP MicroTESK project • Download the MicroTESK demohttp://hardware.ispras.ru IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Contacts • Institute for System Programming of RAS (ISPRAS)http://www.ispras.ru • Hardware Verification R&D @ ISPRAShttp://hardware.ispras.ru • Alexander Kamkinkamkin@ispras.ru IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia

RAS ISP Thank You!Questions? IEEE East-West Design and Test Symposium - September 18-21, 2009 - Moscow, Russia