Interrupts in ARM: Modes & Privileges

190 likes | 212 Vues

Learn about Polling vs. Interrupt, ARM Cortex-A modes, privilege levels, context switching, and interrupt handling in ARM processors.

Interrupts in ARM: Modes & Privileges

E N D

Presentation Transcript

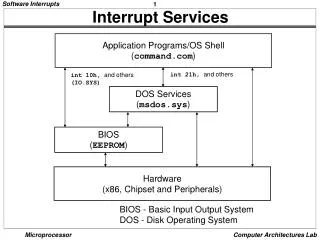

Contents • Polling Vs. interrupt • Interrupt (Exception) in ARM • FIQ interrupt in Raspberry Pi • ARM Cortex-A modes • Privilege levels in ARM • Steps in executing an interrupt • Context switching • Interrupt priorities

Polling Vs. Interrupt Polling Ties down the CPU Interrupt Efficient CPU use Has priority Can be masked

Interrupt in ARM CPSR:

Privilege Importance • Different programs should have different privileges • Memory access example: • A user (application) program should have limited access to memory otherwise it can change the data for other programs and damages them or causes the system to crash • OS should have access to different parts of memory to be able to allocate memory and free it.

Privileged vs. Unprivileged Privileged Unprivileged cannot execute some of the ARM instructions has no access to some registers such the special function registers • can execute all the ARM instructions • has access to all registers

Privileged vs. Unprivileged Privileged Unprivileged has limited access to some regions of memory. is blocked from accessing system timer and system control block • has access to every region of memory • has access to system timer and system resources

Privileged vs. Unprivileged Privileged Unprivileged In Unprivileged mode, one can use SVC instruction to make a supervisor call to switch from Unprivileged level to Privileged level • Interrupt handlers can be executed only in Privileged level

Cortex-A Processor modes • User, • System, • Supervisor, • Abort, • Undefined, • IRQ, • FIQ, • Monitor, • Hypervisor CPSR:

Mode and privilege changes • When the system resets, it is in Supervisor mode and it has the privilege to access the different parts of the system to initialize them. • The OS changes the mode to User when it runs an Application program to limit the privilege of the Application program. • Whenever an interrupt occurs or the Application makes a system call, the mode changes to a privileged mode and OS services the interrupt.

Context Switching in Cortex-A • Every mode has its own stack pointer. So, there is a separate stack for each mode • The registers which are in gray boxes are banked (the mode has its own register) • In all modes, except user/system modes there is a SPSR register which is used to save the value of the CPSR register. • In System mode, the general purpose registers are the same as the User mode.

Processing interrupts in ARM • CPSR is saved in the SPSR of the target mode. • The mode is changed to the target mode. • The IRQ interrupt is disabled by setting the I flag in CPSR. • The current PC is stored in the LR register. • The CPU mode changes to ARM mode. • PC is loaded with the address of the ISR.

Processing interrupts in ARM (Cont.) • From the memory locations pointed to by PC, the CPU starts to fetch and execute instructions belonging to the ISR program. • When the return instruction is executed in the interrupt service routine, the PC register is loaded with the value of the LR and CPSR is loaded with the contents of SPSR. This changes the mode to its previous mode and makes the CPU run the code where it left off when interrupt occurred