Block Diagram

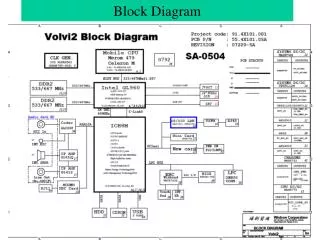

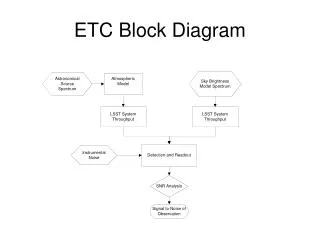

Block Diagram. Volvi2 Clock Block Diagram. Crystal 14.31818MHz. CPU. CLK_CPU_BCLK (166 MHz). X1/X2. CPUT0. BCLK0. CLK_CPU_BCLK# (166 MHz). BCLK1. CPUC0. KBC WPC8763L. PCLK_KBC (33 MHz). Crystal 32.768KHz. PCI4. FWH. PCLK_FWH (33 MHz). PCI3. CLK_MCH_BCLK (166 MHz).

Block Diagram

E N D

Presentation Transcript

Volvi2 Clock Block Diagram Crystal 14.31818MHz CPU CLK_CPU_BCLK (166 MHz) X1/X2 CPUT0 BCLK0 CLK_CPU_BCLK# (166 MHz) BCLK1 CPUC0 KBC WPC8763L PCLK_KBC (33 MHz) Crystal 32.768KHz PCI4 FWH PCLK_FWH (33 MHz) PCI3 CLK_MCH_BCLK (166 MHz) CPUT1_F HPLL_CLK Crestline CLK_MCH_BCLK# (166 MHz) CPUC1_F HPLL_CLK# CLK_MCH_3GPLL (100 MHz) SRCT3 PEG_CLK CLK_MCH_3GPLL# (100 MHz) SRCC3 PEG_CLK# CLK_PCIE_LAN SRCT8 LAN 10/100 Marvell 88E8039 DREFCLK (96 MHz) DPLL_REF_CLK SRCT0/DOTT_96 (100 MHz) Crystal 25MHz DPLL_REF_CLK# DREFCLK# (96 MHz) SRCC0/DOTC_96 CLK_PCIE_LAN# SRCC8 SRCT7 DREFSSCLK (100 MHz) DPLL_REF_SSCLK (100 MHz) DPLL_REF_SSCLK# SRCC7 DREFSSCLK# (100 MHz) CLK_PCIE_MINI1 SRCT4 MINI CARD KEDRON a/b/g/n (100 MHz) REF0 CLK_PCIE_MINI1# SRCC4 (100 MHz) CLK_PCIE_SATA M_CLK_DDR2/# M_CLK_DDR0/# M_CLK_DDR3/# M_CLK_DDR1/# SRCT2 SATA (100 MHz) ICH8-M CLK_PCIE_SATA# SRCC2 CLK_ICH14 (14.318 MHz) CLK14 (100 MHz) DDR2 NORMAL TYPE DDR2 NORMAL TYPE CLK48_ICH (48 MHz) USB_48MHz/FSLA CLK48 CLK_ICHPCI(33 MHz) PCI_F5/ITP_EN PCICLK CLK_PCIE_NEW CODEC ALC268 SRCT1 NEW CARD ACZ_BITCLK (100 MHz) CLK_PCIE_ICH(100 MHz) DMI_CLKN CLK_PCIE_NEW# SRCT6 SRCC1 CLK_PCIE_ICH#(100 MHz) SRCC6 CLKGEN DMI_CLKP (100 MHz) MDC X1/X2 AC_BTCLK_MDC ICS9LPR502 RTC 32.768kHz

Volvi2Power ON/RESET Sequence 5 4 5V_AUX_S5 3D3V_AUX_S5 DDR_VREF_S3 DDR_VREF_S0 AD+ DCBATOUT -3 -4 -6 -5 1D8V_S3 Adapter In PM_SLP_S4# G909 -1 TPS51100 MAX8744 -7 S5_ENABLE -1 S3 S5 PM_SLP_S3# 5V_S5 -2 4 5 3D3V_S5 5 3D3V_AUX_S5 3D3V_S5 1D8V_S3 1D05V_S0 1D5V_S0 PG1 1D8V_S3 10ms after VCCSUS1_05 KBCWPC8763L RSMRST#_KBC RSMRST#_ APL5915 5 TPS51124 PG2 PM_PWRBTN# EN1 EN2 1D8V_S3 KBC_PWRBTN# 2 1D8V_S0 PM_SLP_S3# 6 5 1 PM_SLP_S4# S5_ENABLE 1D25V_S0 -2 3D3V_S5 3D3V_S0 DCBATOUT 1D8V_S0 APL5913 5V_S0 7 PM_SLP_S3# 5V_S5 5 CPUCORE_ON 3 4 PM_SLP_S4# PM_SLP_S3# 2 SLP_S3# RSMRST# SLP_S4# PM_PWRBTN# REGISTER(BTCRL.SBR) PWRBTN# PCIRST# 0:RELEASE 5V_S0 11 1:RESET RTC_AUX_S5 PLT_RST1# VCCRTC ICH8-M 10ms after VCCSUS1_05 PLTRST# TP VCCSUS1_05 HDDDRV#_5 CD ROM 18ms after VCCRTC RTC_AUX_S5 RTCRST# WINDBOND CK_PWRGD VRMPWRGD RTC PWROK CPUPWRGD WPC8768L 9 PWROK 5V_S0 NEWCARD H_PWRGD 3ms after VGATE_PWRGD 99ms after 1D05V_S0 MINICARD RESET# G792 3D3V_S0 LAN VCC_CORE_S0 GOLDFINGER 12 7 8 Crestline 10 VGATE_PWRGD RSTIN# SHDN# PWRGD CPUCORE_ON MAX8770 PWROK H_CPURST# CLK_PWRGD PWRGOOD Merom 13 H_CPURST# CK_PWRGD RESET# CLK ICS9LPR502

Power Budget Block Diagram DDRII 1D8V_S3(5000mA) DDR_VREF__S0(1.2A) Marvell 88E8039LAN 3D3V_LAN_S5(500mA) USB*3 1500mA MDC 40mA KBC Winbond WPC8763L 3D3V_AUX_S5(170mA) KBC EV BD BIOS ROM 30mA 710mA 1D25V_S0 1D25V_S0 1200mA DDR_VREF_S0 DDR_VREF_S0 47000mA VCC_CORE_S0 VCC_CORE_S0 17204mA 1D05V_S0 1D05V_S0 8598mA 1D8V_S3 1D8V_S3 2660mA 1D5V_S0 1D5V_S0 907mA 3D3V_S5 3D3V_S5 50mA 5V_AUX_S5 5V_AUX_S5 1510mA 5V_S5 5V_S5 200mA 3D3V_AUX_S5 3D3V_AUX_S5 1D05V_S0 (Core/I/O) (1131mA) 1D5V_S0 (Azalia/PATA/PCI/PCIE/DMI/ SATA/LPC/USB) (2400mA) 3D3V_S0 (LAN/SPI) (400mA) 3D3V_S5 (SUS) ( 277mA) 5V_S5 (SUS) (10mA) 5V_S0 (USB/PATA/PCI) (6mA) ICH8M Crestline 1D05V_S0 (CORE+GFX) (11310mA)(11573mA) 1D25V_S0 (PLL/DMI)(710mA) 1D5V_S0(TV/CRT) (130mA) 1D8V_S3 (DDRIO/LVDSIO) (3598mA) 3D3V_S0 (TVDAC/CRT Sync/IO/Bandgap) (316mA ) Merom VCC_CORE_S0 (CORE) (47A) 1D05V_S0 (FSB VCCP) (4.5A) 1D5V_VCCA_S0 (PLL) (130mA) 3D3V_S0 3645mA LCD 400mA CLK GENICS 9LPRS502 220mA Mini card 802.11/BT 660mA LPCROM 6mA CODEC 3.3V(35mA) 5V(55mA) Express CARD 1000mA AMP 1410 408mA 5V_S0 5331mA FAN 500mA CRT 500mA HDD 2000mA CD ROM 1500mA AMP 1431 800mA TOUCHPAD 25mA

Volvi2 SMI/SCI/SWI Interface LPC BUS ICH8-M X-Bus KBC WPC8763L FWH ECSCI#_1 GPIO7 ECSCI# GPIO8 PM_SLP_S3# SMI# GPIO01 ECSWI# AC_Link GPIO12 PWUREQ# ACZ_SDATAOUT LID_CLOSE# HDA_SDOUT GPIO07 RSMRST#_KBC AC_IN# GPIO40 RSMRST# GPIO06 MDC CODEC ALC268 PM_PWRBTN# GPIO23 HDA_SDIN1 PWRBTN# ACZ_SDATAIN1 BAT_IN# GPIO12 HDA_SDIN0 GPIO03 3D3V_AUX_S5 ACZ_SDATAIN0 KBC_PWRBTN# VCC_POR# ECRST# Power Switch block RSMRST# G792 THRM/Fan Alert# From S3 state wakeup event: (1) Power Button; (2) WOL ( AC Only ); (3) Embedded Modem ( AC Only ) ;(4) RTC; (5) Lid; (6) Battery Critical

Volvi2 Audio Block Diagram KBC_BEEP KBC WPC8763L ICH8-M ACZ_SPKR AUDIO_BEEP ● CODEC REALTEK ALC268 PCBEEP INT_MIC1_CN MIC2_R MIC2_L LINR_IN_R AC97 MIC1_R MIC1_L LINL_IN_L Mic-In Audio AMP. G1412R CDR CDL CD-GND H.P. Jack Line Out PHONE Line Out MDC CON. Audio AMP. G1431F 2 Watt 2 Watt

Volvi2 SMB Interface 3D3V_S5 5V_S0 3D3V_S0 4D7K 4D7K SMBC_ICH ICH8_M SMBD_ICH 1D8V_S0 1D8V_S0 3D3V_S0 DDR2 DIMM A ID=A0/A1 DDR2 DIMM B ID=A2/A3 CLK GEN ICS 9LPRS502 ID=D2/D3 3D3V_S0 3D3V_S0 5V_S0 10K 3D3V_AUX_S5 Thermal 10K G792 3D3V_AUX_S5 ID=7A/7B KBC_SCL2 VCC KBC KBC_SDA2 BAT_SCL WPC8768L BAT_SDA 5V_AUX_S5 Battery A ID=16/17

Volvi2 SMB Interface 3D3V_S0 3D3V_S0 5V_S0 2.2K 2.2K 10K CRT CLK_DDC1_5 Crestline GMCH GMCH_DDCCLK GMCH_DDCDATA DAT_DDC1_5 CLK_DDC_EDID DAT_DDC_EDID LCD