5.3 สัญลักษณ์และความสัมพันธ์แรงดัน - กระแสของ MOSFET

5.3 สัญลักษณ์และความสัมพันธ์แรงดัน - กระแสของ MOSFET. NMOS. สัญลักษณ์แบบสี่ขา ( 4-terminal symbol). PMOS. Discrete MOSFET.

5.3 สัญลักษณ์และความสัมพันธ์แรงดัน - กระแสของ MOSFET

E N D

Presentation Transcript

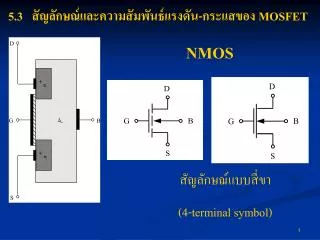

5.3 สัญลักษณ์และความสัมพันธ์แรงดัน-กระแสของ MOSFET NMOS สัญลักษณ์แบบสี่ขา (4-terminal symbol)

Discrete MOSFET สำหรับ discrete MOSFET ผู้ผลิตจะทำการเชื่อมต่อขา S และขา B เข้าด้วยกัน (ดังนั้น discrete MOSFET จะไม่มี body effect) ทำให้เราสามารถใช้สัญญลักษณ์แบบ 3 ขาได้ NMOS PMOS ทั้งนี้จะเห็นได้ว่าขา D และ S ของ discrete MOSFET จะไม่สามารถใช้สลับกันได้

MOSFET ในวงจรรวม อย่างไรก็ตามในบางครั้งเราไม่สามารถทำการเชื่อมต่อ B และ S ของ MOSFET ใน IC ได้ ตัวอย่างเช่น NMOS ทุกตัวภายใน IC ที่ผลิตด้วยกระบวนการผลิตแบบ CMOS n-well มาตรฐานจะมีขา B ร่วมกัน ในกรณีนี้จะนิยมต่อขา B ของ NMOS ไปยังแหล่งจ่ายแรงดันต่ำสุดของวงจร (VSSหรือ ground) เพื่อไม่ให้รอยต่อ pn (ระหว่าง BS และ BD ของ NMOS) มีโอกาสอยู่ในสภาวะ on

ในทำนองกลับกัน PMOS ทุกตัวภายใน IC ที่ผลิตด้วยกระบวนการผลิตแบบ CMOS p-well มาตรฐานจะมีขา B ร่วมกัน ในกรณีนี้จะนิยมต่อขา B ของ PMOS ไปยังแหล่งจ่ายแรงดันสูงสุดของวงจร (VDD) เพื่อไม่ให้รอยต่อ pn (ระหว่าง substrate และขา D/S ของ PMOS) มีโอกาสอยู่ในสภาวะ on

หากมีการระบุว่าขา B ของ MOSFET ต่ออยู่ที่ใด เราสามารถใช้สัญญลักษณ์แบบ 3 ขาแทน MOSFET ใน IC ได้ดังนี้ NMOS PMOS Analog Digital

NMOS หากละเลย Body Effect เราสามารถแสดงความสัมพันธ์ระหว่างiDกับ vGSและvDS ได้ในสามสภาวะ ได้ดังนี้ Surface mobility ของ electron Gate capacitance ต่อหน่วยพื้นที่ โดย (หน่วย A/V2 ) Noteหากละเลย channel-length modulation effect ด้วยiDของ NMOS ในสภาวะ active จะประมาณได้เป็น

PMOS หากละเลย Body Effect เราสามารถแสดงได้ว่า Surface mobility ของ hole Gate capacitance ต่อหน่วยพื้นที่ โดย

ตัวอย่างการวิเคราะห์วงจร MOSFET ตัวอย่างที่ 1 กำหนดให้ NMOS มี K = 0.4 mA/V2และ Vt =2 V จงเลือกค่าตัวต้านทานในวงจรเพื่อให้ NMOS อยู่ในสภาวะ active ID = 0.4 mAและVDS = 4 V และ เนื่องจาก VG = 0 ดังนั้น และ แบบฝึกหัด 1 จงหาว่า RD ต้องมีค่ามากกว่าเท่าไหร่จึงจะทำให้ NMOS อยู่ในสภาวะ triode

ตัวอย่างที่ 2 กำหนดให้ NMOS มี K = 0.4 mA/V2และ Vt = 0.9 V และ RD = RS = 10 kWจงเลือกค่า VGเพื่อให้ NMOS อยู่ในสภาวะ active และมี ID = 0.1 mA และ เนื่องจาก VS = (0.1mA)(10kW) = 1 V ดังนั้น VG = 2.4 V แบบฝึกหัด 2 จงทำการตรวจสอบว่า NMOS อยู่ในสภาวะ active จริงหรือไม่ แบบฝึกหัด 3VGจะต้องน้อยกว่าเท่าไหร่ NMOS ถึงอยู่ในสภาวะ cut-off

ตัวอย่างที่ 3 กำหนดให้ NMOS มี K = 0.2 mA/V2และ Vt = 0.8 V จงเลือกค่า RDเพื่อให้ ID = 0.8 mA NMOS ทำงานอยู่ในสภาวะ active แน่ ๆ (?) และ เนื่องจาก VDS = VGS = 2.8 V ดังนั้น แบบฝึกหัด 4 จงเลือก RDที่ทำให้ ID = 0.5 mA

ตัวอย่างที่ 4 กำหนดให้ NMOS มี K = 0.1 mA/V2และ Vt = 1 V ถ้า RD = 5 kWจงหา ID แทน VGS = VDS = VDD - IDRD = 5 - 5000IDลงในสมการข้างบนจะได้ จะได้ ID = 0.4 mA, 1.6 mA แบบฝึกหัด 5 ถ้า RD = 2 kWจงหา ID

ตัวอย่างที่ 5 กำหนดให้ NMOS มี K = 0.5 mA/V2และ Vt = 1 V ถ้า R1 = R2 = 10 kWและ RD = RS = 6 kW จงหา ID แทนVG = 5 V และ VS = IDRD = 6000IDลงในสมการข้างบนจะได้ จะได้ ID = 0.5 mA, 0.89 mA VDS = 4 V

NMOS Inverter ถ้าเราแทนที่ RDด้วย NMOS ที่ทำการลัดวงจรขา D และ G NMOS จะอยู่ในสภาวะ active เสมอเพราะ vGS > vGS - Vtn vDS > vGS - Vtn = Veff

ในช่วง A-B’ M1 cut-off ทำให้ iD1 = iD2 = 0,

0<vI<Vtn MP อยู่ในสภาวะ triode โดย K(2VeffP-vSDP)vSDP = 0 vSDP = 0 VDD-|Vtp|< vI < VDD MN อยู่ในสภาวะ triode โดย K(2VeffN-vDSN)vDSN = 0 vDSN = 0

CMOS Inverter VDD

ย่าน II เมื่อเพิ่ม vIจะทำให้ vOตกลงและ MPอยู่ในสภาวะ triode จนกระทั่ง ย่าน IV เมื่อลดvIจะทำให้ vO เพิ่มขึ้นและ MNอยู่ในสภาวะ triode จนกระทั่ง MP เข้าสู่สภาวะ active ย่าน III MN เข้าสู่สภาวะ active

แบบฝึกหัด 6 รูปข้างล่างแสดงกราฟโอนย้ายแรงดันของวงจรกลับตรรกะ CMOS ที่มี VDD = 5 V ถ้า จงหาว่า vIในช่วงใดที่ทำให้ 1) MN/cut off และ MP/triode(2) MP/cut off และ MN/triode