Enhancements and Availability of High-Performance Components for GOLD Design Update

The latest GOLD design update, effective February 2, 2010, introduces significant enhancements for high-performance components. The Xilinx XC6VHX380T will be available throughout the GOLD's lifecycle, offering over double the link bandwidth per FPGA/module compared to previous designs. New Avago parallel opto transmitters and receivers enhance signal integrity. Key modifications include updated pinouts, pre-emphasis on the receiver interface, and equalization on the transmitter interface. The design retains half of the existing GOLD layout while introducing upgraded components for improved performance.

Enhancements and Availability of High-Performance Components for GOLD Design Update

E N D

Presentation Transcript

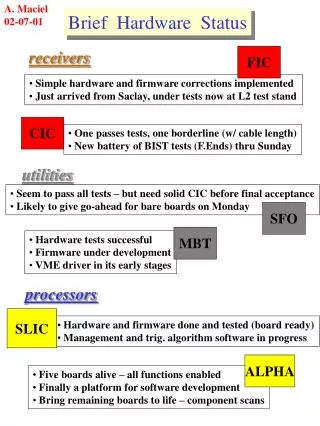

Hardware status GOLD Update 02 Feb. 2010

GOLD design changes Availability of high performance components : • Xilinx XC6VHX380T will become available during lifetime of GOLD This more than doubles xGb/s link bandwidth per FPGA / Module (higher aggregate bandwidth than on single ended I/O) • New non-SNAP12 parallel opto transmitters and receivers (Avago) • exhibit better signal integrity • Modified pinoutwrt SNAP12 • pre-emphasis on receiver electrical interface • equalization on transmitter electrical interface • Seem to be cost effective Modify GOLD design • Keep half the GOLD as shown in Heidelberg • Equip the other half with XC6VHXT rather than XC6VLXT • Wire the added xGB/s connectivity to ATCA backplane • Build additional opto module for Avago receivers

GOLD floor plan • Z3 • V • Modification: • Discard bottom four XC6VLX and replace by XC6VHX (H) • ES silicon of 72-link devices expected to be available soon (48*6.5+24*11) Gb/s • Add multigigabit links in zone 2 (equiv. 22300 bit / BC) • standard Z2 connectors have been reported to support 10Gb/s • V • Opto • V • V • M • Z2 • H • H • 890Gb/s • total • H • H • Z1

Test daughter • Build two versions:SNAP12 and AVAGO • Half size module • 3* opto receive • 36 * fanout (*2, CML) • 2 FMC connectors • 3 * opto transmit • control CPLD