Update on GOLD Hardware Status - March 2010

The GOLD hardware project is progressing, with updated floor plans and schematics in the works. The current design includes multi-gigabit links in Zone 2 and high-speed capabilities with a total throughput of 890 Gb/s. While routing for high-speed links is hand-routed, lower-speed links are set for auto-routing. Component procurement is underway, with deliveries expected for AVAGO and Xilinx parts. Firmware activities focus on extending VME bus capabilities through the GOLD system. Continued monitoring of production timelines is crucial as overall project development unfolds.

Update on GOLD Hardware Status - March 2010

E N D

Presentation Transcript

Hardware status GOLD Update 03 Mar. 2010

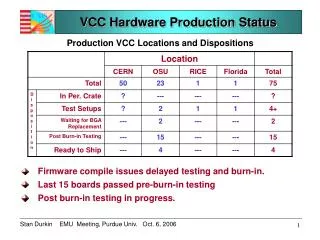

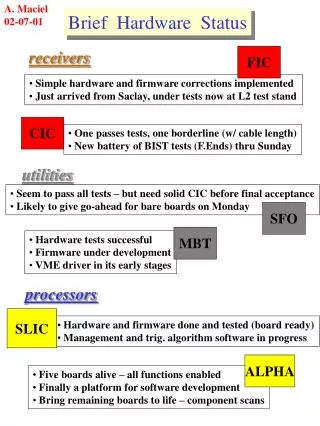

GOLD floor plan(approximate) • Z3 • L • 5 * XC6VLX (L,M) • 4* XC6VHX (H) • 144 multigigabit links in zone 2 (equiv. 22300 bit / BC) • L • Opto • L • L • M • Z2 • H • H • 890Gb/s • total • H • H • Z1

GOLD – current status • Schematics partially done • Routing as shown: • xGb/s links hand routed • ‘Low’ speed links (1Gb/s) to be auto routed

GOLD status • Schematics and layout under way • Components ordered. Lead time: • AVAGO (2*T, 2*R) : arrived • SNAP12 : mid April • Xilinx XCVLXT: 8-10 weeks • Production of Xilinx HXT devices delayed Firmware activities: Currently working on extension of VME bus from 9U processor crates, via BLT module, optically into GOLD