Radiation Tolerant Circuitry

90 likes | 255 Vues

Radiation Tolerant Circuitry. Project Objective

Radiation Tolerant Circuitry

E N D

Presentation Transcript

Project Objective In order to improve the reliability of deep sub-micron digital designs, especially for the electrical facilities exposed to various radiations in outer-space, we are going to analyze combinational and sequential logic circuits, in order to evaluate the performance in different fields.

Motivation Space Environments Single Event Effects Single Event Upset Single Event Transient Scaling of CMOS Technologies

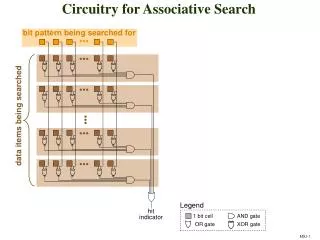

Methodology I– Fault-tolerant techniques Logic styles: guard-gate CVSL etc. Redundancy: Dual redundancy Triple redundancy

Methodology II – Sequential Logic Circuits Flip-Flops SR-Latch based FF DICE-based FF CVSL based FF Guard gate based FF Sense amplifier based FF Performance: Latch-time, setup time, hold time, power, etc. Critical charge

combinational logic circuits such as adders or multipliers will be designed with different fault-tolerant techniques, such as guard-gate, CVSL logic Methodology III – Combinational Logic Circuits Circuits: 8-bit adders/multiplier Performance: Speed, power, etc. Critical charge

Methodology IV – Layout Guard-ring Guard-drain

Schematic presenting basic concept of the original CREST design. Schematic presenting new SET evaluation approach implemented as C-CREST Methodology V – Testing Autonomous error test structure The Crest & C-Crest autonomous architecture