13 . Pulsed waveforms and Timing Circuit Design

200 likes | 557 Vues

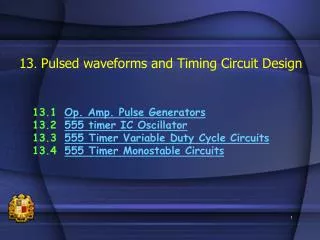

13 . Pulsed waveforms and Timing Circuit Design. 13.1 Op. Amp. Pulse Generators 13.2 555 timer IC Oscillator 13.3 555 Timer Variable Duty Cycle Circuits 13.4 555 Timer Monostable Circuits. 13.1 Op. Amp. Pulse Generators. Study example 14.7-page786 for this pulse generator with diode.

13 . Pulsed waveforms and Timing Circuit Design

E N D

Presentation Transcript

13. Pulsed waveforms and Timing Circuit Design 13.1 Op. Amp. Pulse Generators 13.2 555 timer IC Oscillator 13.3 555 Timer Variable Duty Cycle Circuits 13.4 555 Timer Monostable Circuits

13.1 Op. Amp. Pulse Generators Study example 14.7-page786 for this pulse generator with diode

Summary of Design Equations Op. Amp. Pulse Generators

Example: Given the Op. Amp. Pulse Generator circuit below, (a) calculate and sketch the output waveform (b) frequency output and (c) duty cycle of the output waveform if C = 0.1mF, R = 20kW, R1= R2= R3= 1kW.

Example: Design the Op. Amp. Pulse Generator circuit to generate a 500Hz waveform at a duty cycle of 20%. (a) Sketch the output waveform (b) Design all charging and discharging resistors if C = 0.1mF and voltage divider resistors R1= R2= 1kW to provide threshold voltage to the generator.

If pin 4 (Reset pin) is less than VCC, PNP BJT conducts and (R) becomes high to reset the Flip-flop Discharge pin 7 is zero if Reset and floats if Set Output is zero if Reset and high (VCC) if Set Comparators More positive applied to the positive terminal (or more negative applied to the negative terminal will make output high RS-Flip-flop Reset(R) or Set(S) with logic high input 555 Timer 13.2 555 timer IC Oscillator

5. If Modulate pin 5 is connected to a dc source or to external resistor, pin 2 and pin 6 levels will be no longer 1/3 or 2/3 of VCC but will be changed to any other levels. 1. If Threshold pin 6 is more than 2/3 of VCC, “R” will be high and output Q is Set to zero 3. If Trigger pin 2 is less than 1/3 of VCC, “S” will be high and output Q is Set to VCC 2. If Threshold pin 6 is less than 2/3 of VCC, there is no change at output Q 4. If Trigger pin 2 is more than 1/3 of VCC, there is no change at output Q

#1. Let pin 3 is set (=high). Pin 7 will float. Then C is charged to VCC through R1+R2=RC #2. But VC is never charged to VCC because when VC=just above (2/3)VCC pin 6 takes care and the output pin 3 will reset. #3. When pin 3 is reset(=low). Pin 7 will be zero. Then C is discharged to 0 through R2=Rd #4. But VC is never discharged to 0 because when VC= just below (1/3)VCC pin 2 takes care and the output pin 3 will set. It repeats step #1 again. Astable Multivibrator (pulse generator)

Continuous and step Pulse frequency Discharge R2 is varied to get continuous change of discharge time td which will vary both frequency and duty cycle R1 is varied to change charge R1 + R2 to get continuous change of charge time tc which will vary both frequency and duty cycle Decade step of capacitor C1 =10C2 , C2=10C3 is switched to get step change of “T” which will vary the frequency but duty cycle remains the same

13.3 555 Timer IC Variable Duty Cycles Circuits By using a diode to bypass R2 while charging the capacitor, the tc is found from R1 alone and td is found from R2 alone. Now tc= CR1ln2 and td = CR2ln2 Duty=(CR1ln2)/(CR1ln2 + CR2ln2 ) = R1/(R1+R2) If R2 = R1 then duty cycle = 50% If R2 > R1 then duty cycle > 50% If R2 < R1 then duty cycle < 50%

#1. Let pin 2 is high and pin 3 is low. Pin 7 will zero. Output is also zero. Then C is also discharged to 0 through pin 7 #2. When pin 2 is triggered to zero for a short time, Pin 3 will be high. Then pin 7 is floating. #3. Now C is charged to VCC through R. Output pin 3 is then high #4. But VC is never charged to VCC because when VC= just above (2/3)VCC pin 6 takes care and the output pin 3 will reset. And it stays stable at reset all the time until another external trigger. Monostable Multivibrator (timer) 13.4 555 timer IC Monostable Circuit

Summary of Design Equations 555 Oscillator and Timer Astable Multivibrator 1 Astable Multivibrator 2 Astable Multivibrator 3 Monostable Multivibrator

Example: Design the 555 Timer IC Pulse Generator circuit to generate a 500Hz waveform at a duty cycle of 80%. (a) Sketch the output waveform (b) Design all charging and discharging resistors if C = 0.1mF (c) Sketch the circuit.

Example: Design the 555 Timer IC Pulse Generator circuit to generate a 500Hz waveform at a duty cycle of (a) 50%. (b) 20% (c) 80% Design all charging and discharging resistors if C = 0.1mF (c) Sketch the circuit.

Example: Design the 555 Timer IC Pulse Generator circuit to generate a 20Hz to 250Hz waveform by using a minimum discharge resistance of 1kW. (a) Sketch the output waveform (b) Design all charging and discharging resistors if C1 = 0.1mF (c) Sketch the circuit (d) what is the maximum frequency of this generator if a decade step uses 2 more capacitors C2=0.01mF, C3=0.001mF?

Example: Design the 555 Timer IC circuit to generate a 100ms pulse. (a) Design C if charging resistors is 1MW (b) Sketch the circuit.