Amplifier and Feedback Circuit Design

190 likes | 527 Vues

Amplifier and Feedback Circuit Design. Philip Burrows Queen Mary, University of London On behalf of: Colin Perry Oxford University. FONT1 (i). needed amplifier to drive kicker at NLCTA had to be fast relative to 170ns bunch train wanted as much drive as could readily get

Amplifier and Feedback Circuit Design

E N D

Presentation Transcript

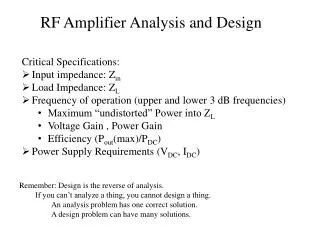

Amplifier and Feedback Circuit Design • Philip Burrows • Queen Mary, University of London • On behalf of: • Colin Perry • Oxford University Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT1 (i) • needed amplifier to drive kicker at NLCTA • had to be fast relative to 170ns bunch train • wanted as much drive as could readily get • had to be done quickly and easily Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT1 (ii) • chose planar triode vacuum tubes as easiest way (type Y690A) • single output tube @ 5kV gave +/-8A into 50 ohms • two more tubes (ac coupled) to get enough gain • fast op-amp (THS3001) added later for more gain • tubes turned on for ~10us by IGBTs in cathode circuit • 18A from 5kV when on = 90kW • but mean HV power at 10Hz = 10W • IT WORKED: risetime ~10ns, delay ~16ns • BUT: large (400 x 300 x 120mm) • poor linearity and pulse shape • inadequately engineered and probably unreliable • …and no-one keen on working on unit with 5kV supply and big capacitors if it could be avoided. Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT2 (i) • repeat of FONT1 at NLCTA • aims: • modest increase in overall speed • better quality data • similar amplifier output and speed sufficient • requirements: better quality and usability Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT2 (i) • able to go solid-state because of: • the HV RF MOSFETs from Directed Energy Inc (now part of Ixys) • similar to usual switching MOSFETs • optimized for RF • RF type low-inductance package • chosen device: 500V max, usable to 25A • design of SLAC kicker • strips connected internally at one end • connect with very short (120mm) cables • drive with current source into an inductive load (200nH total) peak drive voltage reduced to +/-100V for +/-8A • cf: +/-400V for +/-8A into 50 ohms • NB design of kicker gives only magnetic deflection, so reduced voltage does not reduce sensitivity Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

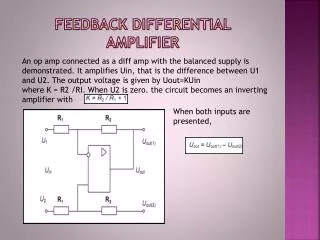

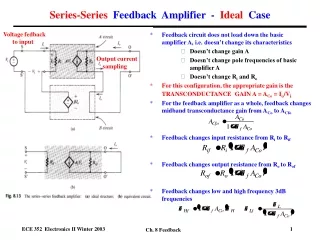

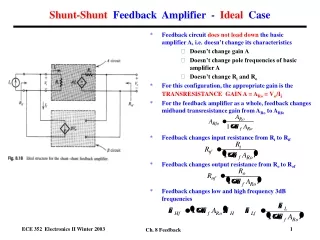

FONT2 (iii) • output stage: • differential (push-pull) pair of MOSFETs • a little source degeneration • centre tapped choke feeding 200V to drains • differential output drive to kicker • driver stage: • effective input C of FETs ~500pF • low Z (low R and low L) driver needed • 10 high speed op-amps as buffers parallelled to drive each gate • 2 op-amps as phase-splitting gain stage to drive buffers Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT2 (iv) • turning on output stage: • when ‘on’, draws 25A @ 200V = 5kW • FETs can’t take this continuously • so as in FONT1, turn on for ~10us • 1W DC/DC converter enough for 200V supply • no heatsink needed for FETs • FETs normally biassed ‘off’ by drivers • turn on by 10us pulse into both sides of phase splitter • pulse takes gates of both FETs positive turning them on • possible because the op-amps can give 15V swing Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

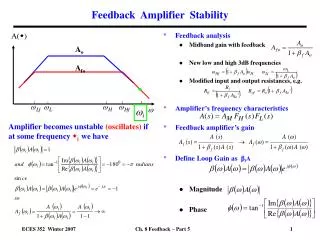

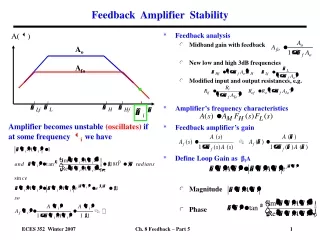

FONT2 (v) • IT WORKED: • current and timing much as FONT1 (+/-8A, 12ns risetime, 16ns delay) • good pulse shape, stable, easy to use • small (160 x 100 x 50mm) • 2 were used in FONT2, into 2 kickers for increased deflection • PROBLEMS: • some instabilities at 200 to 300MHz • voltage gain very high when load impedance became resonant • cured by adding RC stabilizing networks Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT3 (i) • a similar feedback experiment at ATF • much shorter bunch train meant reducing all delays • target for delay through kicker amplifier: 6ns • output drive sacrificed to do this with reasonable effort • design based on FONT2 • same MOSFETs • differential drive to kicker • similar op-amp based driver • modified to increase speed and for different kicker Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT3 (ii) • kicker now driven more conventionally, matched to its cables • at small gaps (needed for sensitivity) ~50 ohms differential • matches a pair of 50 ohm coax in parallel to each side (except for connector and feedthrough section) • kicker terminated in two pairs of 50 ohm cables, 10m long • 200V to output is fed from far end (eliminating tapped inductor) • MOSFET stage has 25 ohm load resistors back-terminating the cables • these take half output current, leading to +/-4A to kicker • greatly improve stability • slightly improve delay • and anyway, FETs couldn’t safely stand voltage of full current swing into kicker (+/-8A into 25 ohms = +/-200V) Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT3 (iii) • driver stage changed in detail: • now 16 OPA693 gain of 2 buffers to drive each gate • faster (700MHz vs 300MHz) & smaller (sot23-6 vs so-8) • OPA695 in phase splitter: also faster • both types have a ‘power-down’ pin • turned on along with output stage • simplifies power supply & avoids need for heatsink • turning on output stage: • changed because op-amps limited to +/-6V supplies • not enough swing to turn off FETs completely • drive capacitively coupled to gate • turn-on bias pulse fed to gate through resistor and inductor • output is turned on for 5us: conditions stable after 3us Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT3 (iv) • IT WORKS (or seems to, so far…): • small size: pcb 90 x 100mm (with front end 160 x 100 x 25mm) • good pulse shape • risetime 6.5ns, delay 6ns • A Note on Speed Issues • figures are with HF compensation in driver and output to boost speed • the FETs have a bit more source inductance than suggested by datasheet • this is the worst factor in limiting speed • a higher drive voltage would have been a better choice • a good solution would have used a pair of low voltage RF FETs as driver • a cascode configuration looked good and was considered: rejected as needing too much development time • planar triodes still probably offer the highest performance, but would take a much greater engineering effort Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

Front-end Feedback Circuits (i) • basic requirements: • additional gain for the low level BPM output • remotely controlled gain in the main loop • remotely controlled gain in the delay loop • sum the main and delay loop signals • disable the delay loop until just before the bunch train • remotely controlled delay round the delay loop is needed • FONT has always used a simple relay box switching cable delays • will not be discussed further Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

Front-end Feedback Circuits (ii) • FONT1 and FONT2: • front end design was easy, based on AD835 multiplier chip: • a nice variable gain stage • includes summing function • 250MHz bandwidth • switching the gain control input to zero disables the loop • FONT3: • much harder, to keep delay low • AD835 too slow (~3ns) • slightly exotic amplifiers needed • as built: total delay ~1ns • it is combined with the power amplifier board in a unit 160 x 100 x 25mm Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

Front-end Feedback Circuits (iii) • for FONT3 we have: • variable gain: pin diode attenuators • current controlled passive devices, delay ~0.1ns • gain stages: THS4302/THS4303 amplifiers • op-amps with internal feedback resistors • voltage gains x5/x10, closed loop bandwidth 2.5/1.8GHz • SiGe parts in QFN16 package • 2 x10 stages in main loop path, 2 x5 in delay loop • loop disable: ADG901 CMOS RF switch • switches in ~3ns • bandwidth to ~3GHz • switching transient on output <0.5% peak signal level Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

Front-end Feedback Circuits (iv) • and also in FONT3: • variable HF boost in main loop path (with variable capacitance diode) • compensates for main output stage response • variable HF roll-off in delay loop path (with variable capacitance diode) • matches response of delay loop to main loop via power amp • variable LF boost in main loop path (preset by solder links) • to correct for droop in pulse response • low pass filter on input • final part of BPM processing • provision for adding output from an AWG to input signal • to allow a non-zero position reference profile to be defined Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

Amplifier + Feedback Board Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05

FONT3 kicker system in total • front end and kicker amplifier (as described) • variable delay box (15ns range, in 1ns steps) • HV supply • 12V to 200V DC/DC converter + 35uF plastic film output capacitors • support box (close to amplifer) • generate supply voltages (from 24V in) • timing to turn on amplifier and loop (from 2 NIM inputs) • test pulse and monitor outputs • interface to other control lines • control box (located remotely) • manual control through pots and switches, and supplies power • (was to be uC unit at the amp: dropped because of risk to schedule) • It all (with 50m control cable, 2nd amplifier unit, spares, tools, and documentation) went in a suitcase without an excess baggage charge Philip Burrows Third Mini Workshop on Nano Project, KEK 30/5/05