Decimation Filter (Accumulate-and-Dump)

Decimation Filter (Accumulate-and-Dump). Howard Chen Keng-Han Chuang Ed Stricker William Tsoi Advisor: Dave Parent May 11, 2005. Abstract. The circuit adds four 8-bit words, then latches to the output the 8 most significant bits of the 10-bit result.

Decimation Filter (Accumulate-and-Dump)

E N D

Presentation Transcript

Decimation Filter(Accumulate-and-Dump) Howard Chen Keng-Han Chuang Ed Stricker William Tsoi Advisor: Dave Parent May 11, 2005

Abstract • The circuit adds four 8-bit words, then latches to the output the 8 most significant bits of the 10-bit result. • We designed an 10-bit CLA adder, 2 sets of DFF latches, a divide by 4 frequency divider and a reset circuit. The operation frequency is 200 MHz, it uses 80mW of Power and occupies an area of 205x158mm2

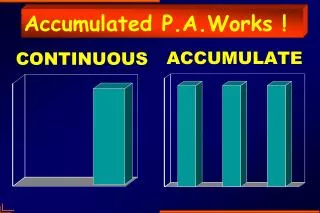

Introduction In an ADC sometimes there is a need to average the output to simplify the circuitry after and lower power consumption. A set of latches accumulates K inputs from the adder. The result of K inputs is then dumped into the output latches. At the same time the first set of latches are reset to zero to start the process over.

Introduction • The word size for this circuit is 8-bit, after K add cycles only the 8 MSB bits are sent to the output so that the result is an average of the K inputs. • Our clock speed is 200 MHz, and the K value is 4.

8 10 8 8 Input Latches_2 Output 10 Latches_1 Clock Reset divide by 4 Block Diagram

Project Summary • DFFs were used for latching the outputs from the adder as well as the final output. • A circuit composed of a NAND gate and inverters is used to implement the reset function. • A CLA (Carry Look Ahead) adder is used for addition.

Project Details • TSPC (True Single-Phase Clock) DFFs were used exclusively (text p.399) for the latches and frequency divider. • A CMOS pair was inserted to implement reset function • These are fast and only use 11 to 13 transistors • The reset circuit consists of a three input NAND gate, an inverter for the output, an inverter for the fs/2 input, and a double inverter to buffer the clock input. • The circuit outputs a high once every 4 clock cycles when all three inputs are high • The three inputs are system clock, fs/2 and fs/4

Project Details • The add portion consists of two 4-bit and one 2-bit CLA adder chained together. • The first 4-bit is designed for carry out only, no carry in. • The second 4-bit has both carry in and carry out. • The carry out of the 2-bit adder is the tenth bit.

Cost Analysis • Estimate how much time you spent on each phase of the project • verifying logic 60hr. • verifying timing 20hr. • Layout 60hr. • post extracted timing 20hr.

Lessons Learned • The circuit worked at 200MHz in schematic but was slower in layout because of interconnection lengths. Better planning for layout could have helped maintain speed. • The size of this project may be too ambitious for a 166 class.

Summary • This project was a good experience for learning circuit design with CAD tools as well as project planning and execution.

![[PDF] Free Download Fix-It and Forget-It Slow Cooker Dump Dinners and Desserts By Hope Comerford](https://cdn4.slideserve.com/7970954/slide1-dt.jpg)