Standard cell based criptographic ASIC resistant to side channel attacks

130 likes | 302 Vues

LABORATORY FOR ELECTRONIC DESIGN AUTOMATION Faculty of Electronic Engineering University of Nis. Standard cell based criptographic ASIC resistant to side channel attacks. Authors : MILENA STANOJLOVI Ć PREDRAG PETKOVIĆ. Overview. Introduction Strategies against SCA

Standard cell based criptographic ASIC resistant to side channel attacks

E N D

Presentation Transcript

LABORATORY FOR ELECTRONIC DESIGN AUTOMATION Faculty of Electronic Engineering University of Nis Standard cell based criptographic ASIC resistant to side channel attacks Authors: MILENA STANOJLOVIĆ PREDRAG PETKOVIĆ

Overview • Introduction • Strategies against SCA • Hardware protection of DPA • Resistance to SCA WDDL and NSDDL cells • Conclusion

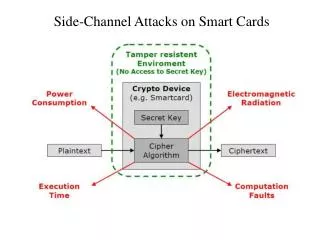

Introduction Data protection is very important in everyday life and for that reason cryptography received a significant position. Important information and secret keys can be obtained by analyzing consumption encrypted hardware. Some of the methods that allow easier breaking of codes known as SPA (Simple Power Analysis), DPA (Differential Power Analysis) and EMA (Electromagnetic Analysis).Common to all these methods is analysis of information that leaks from physically implemented hardware.

Strategies against SCA Attacks which make use of such inherent physical leak-age are called side-channel attacks (SCA). SCA pose a major threat because the physical implementations of the cryptographic devices are difficult to control and often result in unplanned leakage of information. Typically, side-channel attacks do not require the device to be opened or access to internal parts of the system.

Strategies against SCA The countermeasures proposed against DPA can be grouped into three categories: randomizing, masking, and blinding. We are use a blinding method. One class of this method is known as Dual-rail with Pre-charge Logic (DPL). All signals are duplicated and have true and false representations. Good representatives of DPL are WDDL (Wave Dynamic Differential Logic)and NSDDL (No Short-circuit current Dynamic Differential Logic).

Hardware protection of DPAWDDL • Using De-Morgan's laws it can be shown that OR cell is complementary to AND cell. This concept of complementary cells is used in WDDL method. The first picture shows an encrypted AND cell. During pre-charge phase all signals are set to low level. During evaluating phase only exactly one of outputs goes to the high level. Therefore only one load capacitance will charge from VDD.

Hardware protection of DPANSDDL The main difference between NSDDL and WDDL is in the control logic. In addition to pre-charge phase and evaluating phase, phase of capacitor discharge (dis-charge phase) is introduced to. During pre-charge phase signals PRE and DIS are set to low logic level. Evaluating phase occurs when the PRE signal reaches a high logic level. Dis-charge phase lasts as long as both PRE and DIS signals are at high logic level.

Resistance to SCAWDDL and NSDDL cells Three types of cells are simulated. First two cells are designed using WDDL method. The first cell is designed based on standard cells. This cell gave worse results compared to second cell in which the dimensions of transistors are optimized. Therefore the first cell will be excluded from further consideration. The third cell is designed using NSDDL metod. In this case similar results are obtained as with the second cell. Also power consumption increased as it was expected.

Resistance to SCAWDDL and NSDDL cells • Resistance to SCA is tested for following conditions: • mismatchedloads, • extremlyincreased temperature, • different duration of falling and rising edges of inputs signals • extreme changes of power supply voltage (Vdd)

Resistance to SCAWDDL and NSDDL cells Influence of mismatched loads to relative change in energy for a) oWDDL i b) NSDDL AND cells Influence of extreme temperature and signal dinamics to relative change in energy for a) oWDDL i b) NSDDL AND cells

Resistance to SCAWDDL and NSDDL cells All results indicate that the NSDDL cell is more resistant to SCA than optimized WDDL cell. Influence of extreme values of Vdd to relative change in energy for a) oWDDL i b) NSDDL AND cells

Conclusion Cryptography hardware methods for DPA protection are based on designing structures with power consumption independent of input signals dynamic. Physical implementation of WDDL method is very hard to achieve because it requires perfectly matched loads. This problem is resolved in NSDDL method by introducing Dnor circuitry.