Software Defined Radio

Software Defined Radio. 長庚電機通訊組 碩一 張晉銓 指導教授 : 黃文傑博士. Outline. Digital Hardware Choices Hardware Elements DSP Processor Field Programmable Gate Arrays Trade-Offs in DSP, FPGA and ASIC. Digital Hardware Choices.

Software Defined Radio

E N D

Presentation Transcript

Software Defined Radio 長庚電機通訊組 碩一 張晉銓 指導教授:黃文傑博士

Outline • Digital Hardware Choices • Hardware Elements • DSP Processor • Field Programmable Gate Arrays • Trade-Offs in DSP, FPGA and ASIC

Digital Hardware Choices • Flexibility-Overall system clock rate be adjustable in different data rate • Modularity-allow easy replacement or upgrading of subsystem • Scalabilityallow the radio to be enhance to improve capability (increase channels) • Performance • Power consumption, cost ,computational capability metrics

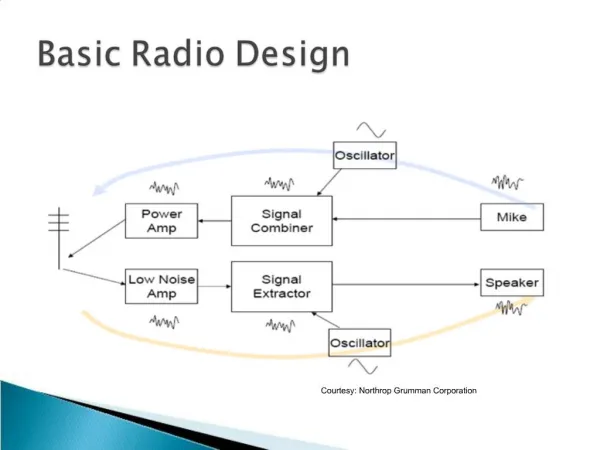

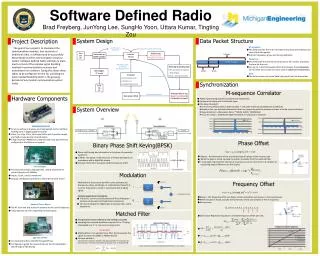

Hardware Elements • DSPs:microprocessor-based, support high level languages like C, offer the most flexibility • ASICs:circuit in fixed silicon ,optimized speed and power consumption, requires sophisticated circuit design and layout software tools. • FPGAs: provide much hardware-level reconfigu-rability, flexibility: DSP>FPGA>ASIC. Tools for FPGA are similar to those for ASIC Trade: flexibility, processing speed and power consumption

DSP Processor • Digital Signal Processors,DSPs are designed to include special functional units in the hardware as well as special instruction in the microcode • FFT or Viterbi decoding • Consists arithmetic logic unit (ALU), accumulator MAC unit and data and address buses • For wireline and wireless communication ,or general control application

DSP Architecture • Harvard Architecture • Program memory and data memory • On-chip or off-chip memory • Uniscalar Architecture • More than one multiplier and ALU • Execution of one instruction per cycle • Single Instruction Multiple Data (SIMD) • Very Long Instruction Word Architecture • Superscalar Architecture • Hybrid Architectures

Numeric Representation • Fixed Point • Less power and cost • Floating Point • Easy to program than fixed point DSP

Pipelining • Pipelining is setting up and executing in parallel the various stages of instruction processing

Field Programmable Gate Arrays • Optimized for multilevel circuit • Static random access memory (SRAM) • SRAM-based FPGA can be reprogrammed and on-the-fly during the operation of the sys.

Application of FPGA to software Radios • System with high sample rate • System with very-high-order FIR filters because the algorithm can be implemented in parallel • System with fast correlators because the LUT architecture of FPGA provides a fast and efficient way to build correlators

Trade-Offs in DSP, FPGA and ASIC • Low complexity can be solved with DSP • FPGA and ASIC tend to be more useful when the complexity of the problem increases • Using a combination of DSP, FPGA and ASIC.

End • Thank you for your attention