SOC Design Challenge

SOC Design Challenge. Rajeev Madhavan Chairman and CEO. Communications. Consumer. Computer. Search For Killer Applications …. Search is on for the next killer applications (microprocessor) E.g Combination communications, consumer and computer What do we do in the meantime?.

SOC Design Challenge

E N D

Presentation Transcript

SOC Design Challenge Rajeev Madhavan Chairman and CEO

Communications Consumer Computer Search For Killer Applications …. • Search is on for the next killer applications (microprocessor) • E.g Combination communications, consumer and computer • What do we do in the meantime? 1980’s 1990’s 2000

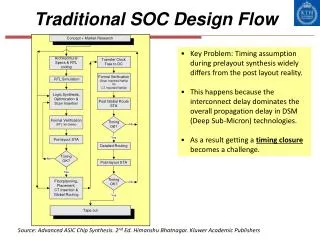

Economy of Scale for Product Company on 300mm Fab ( M US$) 100,000 2001 Revenue 2000 Revenue SC Vendors above $6B Year 2000-14 companies & Year 2001 only- 5 companies. 10,000 Product Revenue from one 300mm Fab (6,000) 1,000 100 10 1 11 21 31 41 51 61 71 81 91 SC Ranking in 2001, 2000 Source: Dataquest (2002)

Economy of Scale for 300mm Fab** • One single 300 mm fab with 30K wafer/month capacity in 90nm will generate about US$6B of product revenue, or about US$2.4B of foundry revenue. ** Cost about US$3B** Handful of product companies and few foundries can afford it or need it. • Joint ventures will be formed** Killer applications (microprocessors) and some other IDMs will have foundries but partnerships in general are evolving Reticle Costs are increasing $1M+ .. But ….

Foundries – Partnerships and Evolutions Moore’s law – Process engineers has delivered at or faster pace Moore’s law will slow not so much technologically, but economically. Disintegration of supply chain continues

Software Development QA Designs IP C++ Quantify Purify Regression/QA C++ JAVA XML Compilers Editing and Debugging Env MANTLE Single Executable Development Costs – Software • Case Study - Magma • Development Environment • Visual C++ • Utilities (Purify, quantify) • Automated QA & regression suite • Purchased available IP • Verilog, VHDL, DEF, GDSII parser • Other parsers • Schematic viewer • About 1.2M lines of code • C++/JAVA

Software Development - Progress Ease of deployment has allowed proliferation of software/IT across the world

Software Investment • Case Study – Magma • Roughly 1.2M lines of code • Synthesis, placement, routing, timing, noise, delay calculation, power rail …. • 65+ Ph.d’s • Low hardware expenses • Total investment - $110M • $80M on R&D

Development Costs - Hardware • Advanced 90nm Complexities • Advanced analysis and hence correction • Optimization with On-chip variation • Multi-mode analysis throughout IC design flow • Complex delay calculation requirement • Slew, skew, hold, setup, multi-corners …. • Noise models, EM models • SPICE delay correlation per path/net • Routing complexities – Manufacturing effects

Hardware - Investment • 40 M gate designs • 18mm X 18mm, 2000 I/Os, 500Mhz • Approximately 4M lines of RTL • Design re-use (wherever possible) • 50+ engineers • Experts in synthesis, P&R, signal integrity, design closure • $80M investment • Requires $160M in 2 years to realize break even • Where is the killer application for this?? Traditional design flows will make Moore’s law economically infeasible

Hardware – Traditional IC creation flows • Series of point tools that looks at various steps • Software does not require every user to look at assembly • Placed gates is too late, netlist is just an intermediate format • Corrections at the end is suicidal • Wireload is completely off and is a non-starter • Standalone analysis is dead • Power and other manufacturing effects cannot be done as point solutions

e.g. placer e.g. router e.g. timer Tool 1 Tool 2 Tool 3 Tool 4 Tool 189 Tool 190 internal datastructure internal datastructure internal datastructure internal datastructure internal datastructure internal datastructure api api api api api api common data base with all data. History – Determining The Design Flow? • Does not leverage similarity • Increases implementation effort • Increases bugs • No consistency by construction • Does not minimize interfaces • Tools spend most code on reading data and conditioning data. Incremental tools (Timer, extraction, noise, rail) are part of the infrastructure. They are not tools!

RTL Goals Process, Library VLSI COMPILER GDS II Design Closure Faster Turnaround Time Least Resources Taming Costs – EDA Advances • Designer spends time doing architecture selection • Verification • Model Checking/assertions • Could become major bottleneck • Implementation • Correct by construction • Flat or Hierarchy • Not driven by tools • Flat • Ease of use • Hierarchy • IP and design management VLSI Compiler – An Economic Necessity

Data-model Timing Alg. External formats or tools Verification Alg. Placement Alg. TCL access Routing Alg. ... GUI access Tool n Alg. Image Snapshot Unified data model – essential for 90nm • Tools share a common data structure. They run directly on it. • All design data lives “in core” during the flow, attached to data structure. • Only one format: the data structure • Allows deep incrementality

“The Tall Thin VLSI Engineer” • Focus on product • Algorithm, functionality and architecture of product • Simplify implementation • Engineering responsibility • Architecture/algorithmic engineer • Is architecture right? • Is design feasible? What is the early silicon performance? • Sign-off to implementation • Implementation engineer • Logistics, implementation, packaging & testing Open EDA system with built in technology Reduce integration needs and meet design goals

Leverage “Give me a lever long enough, and a prop strong enough, and I can single-handedly move the world.” -- Archimedes

Logic design Cellsizing B Wire widening FixedTiming 4X A B Wire spacing SuperCell A 1X Unified Data Model After layout A 1X B Magma’s Technology Edge Fast chips – on time Large designs – on time Quality designs – on time

RTL Netlist Blast Create Blast Plan Blast Fusion Blast Noise Blast Rail GDSII RTL-to-GDSII Solution Netlist Netlist Blast Fusion APX Single executable…multiple product packages Patented unified data model

The Fastest Growing Market IC Implementation Market Share, 2001 • “IC Implementation market will be one of the highest-growing markets in the next 2 years” – expected to be $483M in 2006 • Magma market share currently at 31% and growing rapidly – “grew at a staggering 343% last year” Cadence 24% Synopsys 41% 31% Source: Gartner Dataquest (October 2002)

Conclusion • VLSI Compiler • Productivity gains for digital IC design by leaps • Keeps Moore’s law economically more viable • VLSI Verification • Progress essential for complex designs • Tall thin VLSI engineer • Cost improvement • Productivity improvement • EDA • Change from PD to unified system