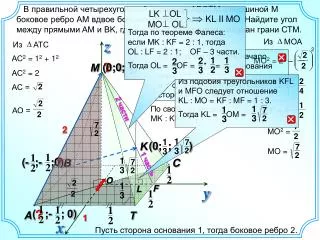

제 2 장 컴퓨터의 논리 회로

제 2 장 컴퓨터의 논리 회로. 컴퓨터의 논리 회로. 강의 내용 디지탈 논리 회로 (Digital Logic Circuit) 논리 회로의 기능 표시 부울 함수 (Boolean Function), 진위표 (Truth Table), 논리 회로도 (Logic diagram) 등 조합 논리 회로 (Combinational Logic) 의 요소 게이트 (Gate) 의 표시와 진위표 완전 집합 (Complete Set) 결선 논리 회로 (Wired Logic, Virtual Logic, Dot Logic)

제 2 장 컴퓨터의 논리 회로

E N D

Presentation Transcript

컴퓨터의 논리 회로 • 강의 내용 • 디지탈 논리 회로(Digital Logic Circuit) • 논리 회로의 기능 표시 • 부울 함수(Boolean Function), 진위표(Truth Table), 논리 회로도(Logic diagram) 등 • 조합 논리 회로(Combinational Logic)의 요소 • 게이트(Gate)의 표시와 진위표 • 완전 집합(Complete Set) • 결선 논리 회로(Wired Logic, Virtual Logic, Dot Logic) • 순서 논리 회로(Sequential Logic)의 요소 • 플립플롭(Flip Flop)과 래치(Latch) • 순서 논리 회로 • 클록 사이클(Clock Cycle) • 순서 논리 회로로서 중앙 처리 장치(CPU)

컴퓨터의 논리 회로 제2장 강의 내용(계속) • 컴퓨터의 기능적 회로 블록 • 반 가산기(Half Adder) • 전 가산기(Full Adder) • 부호 해독기(Decoder) • 멀티플렉서(Multiplexer) • 디멀티플렉서(Demultiplexer) • 레지스터(Register) • 시프트 레지스터(Shift Register) • 계수기(Counter) • 집적 회로(Integrated Circuit) • 범용 대규모 집적 회로(LSI) • ROM - ROM, PROM, EPROM • PLA • 마이크로프로세서(Microprocessor)

디지탈 논리 회로 • 회로 • 아날로그(Analog) 회로와 디지탈(Digital) 회로 • 디지탈 논리 회로(Digital Logic Circuit) • 디지탈 신호(불연속적 신호)로 나타낸 정보를 처리하는 회로 • 예: 2진 디지탈 회로 - 정보는 0과 1 두 가지로 표현 • 2 종류의 디지탈 회로 • 조합(Combinational) 논리 회로와 순서(Sequential) 논리 회로 • 조합 논리 회로 • 출력 값은 입력 값에 의하여만 결정됨 • 예: 게이트(AND, OR, Inverter, NAND, NOR, XOR, 등) • 순서 논리 회로 • 출력 값은 회로의 상태(기억된 정보)와 입력 값에 의하여 결정됨 • 플립플롭(Flip Flop: FF), 래치(Latch) Volt 5 3 1 0 Value 1 undefined Value 0

논리 회로의 기능 표시방법 • 부울 대수(Boolean algebra) • 논리 덧셈 : OR 회로 • 논리 곱셈 : AND 회로 • 논리 부정 : 인버터(NOT) • 부울 함수(Boolean Function) • X = A + B’C (B’ = B ) • Truth Table • Logic Diagram A B X 0 0 0 0 1 1 1 0 1 1 1 1 A B X 0 0 0 0 1 0 1 0 0 1 1 1 A X 0 0 1 1 A B C X 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 1 A B C Z X Y

부울 대수의 액시옴(Axiom) x + 0 = x x . y = y . x x . 0 = 0 x + (y + z) = (x + y) + z x + 1 = 1 x . (y . z) = (x . y) . z x . 1 = x x . (y + z) = x . y + x . z x + x = x x + y . z = (x + y) . (x + z) x .x = x (x + y)’ = x’ . y’ x + x’ = 1 (x . y)’ = x’ . y’ x . x’ = 0 (x’)’ = x x + y = y + x

조합 논리 회로:게이트 도형과 진위표 A B X 0 0 0 0 1 0 1 0 0 1 1 1 X = A・B X = A∧B AND 게이트 A B X X = A + B X = A∨B OR 게이트 A B X 0 0 0 0 1 1 1 0 1 1 1 1 A B X A X 0 0 1 1 X = A 버퍼(Buffer) A X

조합 논리 회로:게이트 도형과 진위표 A B X 0 0 1 0 1 1 1 0 1 1 1 0 X = (A・B)’ X = (A・B) A B NAND 게이트 X A B X 0 0 1 0 1 0 1 0 0 1 1 0 X = (A + B)’ X = (A + B) NOR 게이트 A B X X = A’ X = A A X 0 1 1 0 인버터(Inverter) A X 버블

조합 논리 회로:게이트 도형과 진위표 배태적 OR(Exclusive OR) A B X 0 0 0 0 1 1 1 0 1 1 1 0 X = A ⊕B X =A・B’ + A’・B A B X 배태적 NOR (Exclusive NOR) A B X 0 0 1 0 1 0 1 0 0 1 1 1 X = (A ⊕B)’ X =A’・B’ + A・B A B X

논리 회로의 기능 표시방법 • 부울 함수(Boolean Function) • X = A + B’C (B’ = B ) • Truth Table • Logic Diagram A B C X 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 1 A B C Z X Y • X = A + Y • Y = Z・C • Z = B’ X = A + B’・C

논리 회로의 기능 표시방법 예 X1 A • X = X1 + X2 + X3 • X1 = A・B • X2 = A・B’・C • X3 = A’・C’ X B X2 C X3 X = (A・B) + (A・B’・C) + (A’・C’)

논리 회로의 기능 표시방법 X1 예 2.1 A B X2 X • X = ((A・(B’))’・(B’))’ = (A・(B’)) + B = (A・B’) + B = B + (A・B’) = (B + A) ・(B + B’) = (B + A) ・ 1 = B + A • X = (X1・ X2)’ • X1 = (A・ X2)’ • X2 = B’ • X = ((A・(B’))’・(B’))’ A X B

조합 논리 회로:완전 집합 게이트의 완전 집합(Complete Set) • 서로 다른 게이트의 집합으로 하나의 완전 집합에 속하는 게이트들만 가지고 임의의 논리 기능을 구현할 수 있음 • {I, AND}, {I, OR}, {NAND}, {NOR}, {AND, XOR}, {OR, XOR}, ... (예) • {NOT, OR} A + B = (A’)’ + (B’)’ = (A’・B’)’ • {NAND} AND의 출력 단자에 인버터를 연결 • {NOR} OR 의 출력 단자에 인버터를 연결 (A + B)’ = A’・B’ • {XOR} A・B’ + A’・B = (((A・B’) + (A’・B))’)’ = ((A・B’)’・(A’・B)’)’ • {XNOR} A’・B’ + A・B = (((A’・B’) + (A・B))’)’ = ((A’・B’)’・(A・B)’)’ • 완전 집합과 반도체 장치 기술과의 관계 • 집적 회로: TTL, ECL -완전 집합 • TTL NAND 게이트 • ECL NOR 게이트

부울 함수의 간소화 • 부울 식 • F = xyz + xyz • F = x(yz + yz) = x(y ⊕ z) • 부울 함수의 간소화 • 정리와 가설을 이용한 간소화 방법 • 카노우 맵(Karnaugh Map)을 이용한 간소화

부울 함수의 간소화 (1) 정리와 가설을 이용한 간소화 방법 A B F = AB’ +B • F = AB’ + B = B + AB’ (9) 적용 = (B + A)(B + B’) (14) 적용 = (B + A)・1 (7) 적용 = B + A (4) 적용 = A + B (9) 적용 A F = A + B B

부울 함수의 간소화 (2) 카노우 맵을 이용한 간소화 • 카노우 맵(Karnaugh map) • 사각형으로 된 그림으로 곱들의 합을 단순화 (예) x, y로 구성된 최소항 xy, xy, xy, xy의 카노우 맵

부울 함수의 간소화 【예】부울식을 카노우 맵으로 그려라.

부울 함수의 간소화 • 카노우 맵에서 두 개의 인접된 칸이 1 : 최소항은 두 변수 중에서 하나만으로 표현 가능 [예] xy+xy=(x+x) y = y • 인접하는 네 개의 칸이 1 : 네 개의 최소항은 한 개의 최소항으로 합성

부울 함수의 간소화 【예】부울식을 카노우 맵을 사용하여 간소화

부울 함수의 간소화 F = A’B’ + AB’ + AB 【예】부울 함수를 간소화 B B’ (1) 변수의 개수에 따라 카노우 맵을 만든다 A A’ (2) 주어진 부울 함수의 각 항에 대응하는 카노우 맵의 셀에 1, 0을 기입 B B’ A 1 1 0 1 A A’ B’ (3) 묶인 각 그룹을 OR연산자로 묶는다 F = A + B’

부울 함수의 간소화 • 세 개의 변수를 가진 부울식을 카노우 맵으로 표현 • 여덟 개의 칸이 필요 • 각 칸은 여덟 개의 최소항을 표현 • 인접하는 두 개의 칸이 합성 가능하면 최소화 • 맨 왼쪽 칸과 맨 오른쪽 칸은 붙어 있는 것으로 생각

부울 함수의 간소화 • 인접된 칸 중에서 최대를 구함 • 최대 인접된 칸을 취하는 방법이 다양하므로 구한 최소항도 다양

부울 함수의 간소화 【예】카노우 맵을 사용하여 간소화

부울 함수의 간소화 [풀이]

부울 함수의 간소화 【예】간소화된 회로를 구하라 (1) (2)

부울 함수의 간소화 [풀이]

부울 함수의 간소화 • 네 개의 변수(variable)로 표현된 카노우 맵 • 16개의 칸으로 나누어진다. • 16개의 최소항을 표현

부울 함수의 간소화 【예】카노우 맵을 사용하여 부울식을 간소화

부울 함수의 간소화 [풀이]

결선 논리 회로(Wired Logic) 결선 논리 회로(Wired Logic)-점 논리 회로(Dot Logic) 혹은 가상 논리 회로(Virtual Logic)라고도 부름 • 결선 논리 회로는 능동 소자(active component)를 사용하지 않고 특정한 논리 기능을 구현하는 데 사용됨 • 결선 논리 회로는 특정한 게이트의 출력 단자를 서로 연결한 것임 • 인쇄기판(printed circuit board: PCB)의 면적을 절약할 수 있는 장점 • TTL OC(open collector)와 ECL 게이트, 그리고 3상 버퍼(tristate buffer) 결선 논리 회로의 중요성 버스에 정보를 전달하기 위하여 구동시킬 때에는 각 비트 회선마다 버퍼가 필요한데, TTL(OC) 게이트와 3상 버퍼(tristate Buffer)는 그 자체가 구동기이다.

TTL(OC) 결선 논리 회로:결선 AND 회로 +Volt R A S1 B S2 NAND WL X = (A . S1)’ . (B . S2)’ NAND A S1 B S2 NAND OR X = (((A . S1)’)’ + ((B . S2)’)’)’ NAND A S1 B S2 NAND OR I X = ((A . S1) + (B . S2))’ NAND

결선 논리 회로:3상 버퍼 S S A X A X A S X 0 0 HiZ 1 0 HiZ 0 1 0 1 1 1 A S X 1 1 HiZ 1 0 HiZ 1 0 0 0 0 1 버스 접속 응용 A SA B SB P SP BUS

조합 논리 회로 • 반 가산기(Half Adder) • 전 가산기(Full Adder) • 연산기(ALU) • 부호 해독기(Decoder) • 멀티플렉서(Multiplexer) • 디멀티플렉서(Demultiplexer) • 패리티 비트 발생기(Parity Generator) • 패리티 비트 검사기(Parity Checker) • 부호 변환기(Code Converter)

순서 논리 회로 순서 논리 회로 요소(FF 혹은 래치)를 포함한 논리 회로 플립플롭(Flip Flop: FF) • 1 비트 기억 장소 • 2 가지의 안정된 상태를 가진 장치 플립플롭의 2 가지 안정된 상태(State) 0-상태 1-상태 Q=0 Q’=1 Q=1 Q’=0

순서 논리 회로:SR-래치(SR-Latch) S R I Q’ OR S Q R Q’ SRL OR I Q 특성표(characteristic table) S R Q Comment 0 0 Q0 불변 0 1 0 리세트(reset) 1 0 1 세트(set) 1 1 - 금지 • 비동기적(Asynchronous) 동작 • 입력 변화에 반응 • 많은 수의 FF이 있는 회로의 경우에는 신호 • 전달의 지연시간이 일정하지 않으므로 어느 • FF의 상태가 언제 변하는지 알 수 없기 때문에 • 대단히 위험한 동작임 • 동기적(Synchronous) 동작이 안전

순서 논리 회로:동기(Synchronous) SR-래치 동기 SR-래치(Synchronous SR-Latch) S R AND I Q’ OR S Q R Q’ Clock C SRL OR I Q AND 특성표 S R C Q Q’ 주석 d d 0 Q0 Q0’ 불변 0 0 1 Q0 Q0’ 불변 0 1 1 0 1 리세트(reset) 1 0 1 1 0 세트(set) 1 1 1 - - 금지

순서 논리 회로:D-래치(D-Latch) 동기 SR-래치와 같으나, 입력 단자에 입력 신호가 S=R=1이 되지 못하게 하는 외부 회로가 있음 D E S Q Q R Q’ Q’ D Q E Q’ C DL SRL 특성표 D E Q Q’ d 0 Q0 Q0’ 0 1 0 1 1 1 1 0

순서 논리 회로:D-플립플롭(D-Flip Flop) D-플립플롭은 클록 펄스의 유효한 펄스 전환이 일어나기 직전에 D 입력 단자에 가해진 입력 정보를 기억시킨다. 2 개의 동기 SR-래치를 이용하여 다음과 같이 합성할 수 있다 S2 Q2 Q R2 Q2’ Q’ D C S1 Q1 R1 Q1’ D Q C Q’ C1 C2 SRL SRL DFF 특성표 D C Q Q’ d 0 Q0 Q0’ 0 0->1 0 1 1 0->1 1 0

순서 논리 회로:JK-플립플롭(JK-Flip Flop) JK-플립플롭은 SR-래치의 입력 신호의 값이 S=R=1 인 것을 유효한 입력이 되게 한다. JK-플립플롭은 2 개의 동기 SR-래치를 사용하여 다음 과 같이 합성할 수 있다 J Q C JKF K Q’ S2 Q2 Q R2 Q2’ Q’ S1 Q1 R1 Q1’ AND J K C C1 C2 SRL SRL AND 특성표 J K C Q Q’ 0 0 d Q0 Q0’ d d 0 Q0 Q0’ 0 1 0->1 0 1 1 0 0->1 1 0 1 1 0->1 Q0’ Q0

래치와 플립플롭 • 래치 • 클록 펄스의 유효 레벨에서 데이터 입력 단자에 가해지는 신호의 값을 기억시킴 • 플립플롭 • 클록 펄스의 유효 전환 직전에 입력 단자에 가해지는 신호의 값을 기억시킴 • 데이터 경로의 지연시간을 잘 알 수 없을 때에는 플립플롭이나 래치의 입력 단자에 유효 데이터가 나타나는 정확한 시점을 예측하기 어렵다. • 플립플롭을 사용하려면 클록 펄스의 유효 전환을 언제 시켜야 하는가를 정확히 알아야 하므로 플립플롭은 사용하기가 어렵다. Data clock latch F/F

순서 논리 회로 • 순서 논리 회로 - FF나 래치가 포함된 논리 회로 • 안정된 동작을 위하여는 클록이 필요 • 클록 사이클 FF 조합 논리 회로(tc) FF t1 tc t3 최소 클록 사이클 타임 = (t1 + t2 + t3) = ( (ts + th + td) + tc) FF: Setup time(ts): 유효 클록 펄스 전환 이전에 데이터를 일정한 값으로 유지해야 하는 시간 Hold time(th): setup time 이후에 데이터 값을 일정하게 유지해야 하는 시간 Delay(td): 입력 데이터에 의한 변화가 출력에 나타나는 데 걸리는 시간

순서 논리 회로 - CPU 입력 버스 1 입력 버스 2 레지스터 (순서 논리 회로) 순서 논리 회로 조합 논리 회로 연산 장치 (조합 논리 회로) 출력 버스 1 ( (ts + th + td)REG + tALU ) 최소 중앙 처리 장치 클록 사이클

컴퓨터의 논리 회로 • 조합 논리 회로 • 반 가산기 (Half Adder), 전 가산기(Full Adder) • 반 감산기 (Half Subtractor), 전 감산기(Full Subtractor) • 부호 해독기(Decoder) • 멀티플렉서(Multiplexer) • 디멀티플렉서(Demultiplexer) • 순서 논리 회로 • 레지스터(Register) • 시프트 레지스터(Shift Register) • 계수기(Counter)

컴퓨터의 논리 회로:반 가산기(Half Adder) • 1비트의 두 2진수를 더하는 조합 논리 회로 • 2 입력(A, B)과 2 출력(합 : S, 자리올림 : C)로 구성 • 하단에서는 자리올림 비트를 고려하지 않음 • 연산수(B)와 피연산수(A)의 두 비트로 입력 • 출력은 두 수를 더한 결과인 합(S)과 자리올림 (C)를 발생시키는 회로 • 회로 설계

컴퓨터의 논리 회로:반 가산기(Half Adder) (1) 반가산기는 2진수 1비트를 가산하는 회로 • 회로설계 (2) 더해지는 수, 즉 피연산수의 입력변수를 A, 더하는 수, 즉 피연산수의 입력변수를 B, 출력 변수의 합을 S, 자리 올림을 C로 정의 (3) 진리표를 구한다 (4) 각 출력변수에 대한 간소화된 부울 함수를 구한다 B B’ B B’ A A’ A A’ 1 1 1 S=A’B+AB’=A⊕B C=AB (5) 구해진 부울 함수로부터 논리회로를 그린다 Ai Bi Si Ci

컴퓨터의 논리 회로:전 가산기(Full Adder) • 연산수(B)와 피연산수(A)의 두 비트와 자기 아랫단에서 올라오는 캐리(C0)를 포함하여 세 개의 입력 비트들의 합을 구하는 조합 논리 회로 • 3 입력(A, B)과 2 출력으로 구성 • 회로설계 (1) 2진수 1비트를 가산하는 회로이며 반가산기와는 달리 자기 아랫단에서 올라오는 자리올림,즉 캐리를 포함하여 연산 (2) 더해지는 수, 즉 피연산수의 입력변수를 A, 더하는 수, 즉 피연산수의 입력변수를 B, 자기 아랫단, 즉 하위 비트에서 올라오는 캐리를 C0 ,출력 변수의 합을 S, 자리 올림을 C1으로 정의

컴퓨터의 논리 회로:전 가산기(Full Adder) (3) 진리표를 구한다 (4) 각 출력변수에 대한 간소화된 부울 함수를 구한다 B’C0’ B’C0 BC0 BC0’ B’C0’ B’C0 BC0 BC0’ A’ A A’ A 1 1 1 1 1 1 1 1 S = A’B’C0+A’BC0’+AB’C0’+ABC0 = (A’B+AB’)C0’+(A’B’+AB)C0 = (A⊕B)C0’+ (A⊕B)’C0 = XC0’+ XC0 = X⊕C0 = A⊕B⊕C0 C1 =AB + (A⊕B)C0

컴퓨터의 논리 회로:전 가산기(Full Adder) (5) 구해진 부울 함수로부터 논리회로를 그린다

컴퓨터의 논리 회로:감산기(Subtractor) • 감산기( Subtractor) • 1비트의 두 2진수를 감산하는 조합 논리 회로 • 반감산기 : 2 입력(X, Y)과 2 출력(차 : D, 자리빌림 : B) 전감산기 : 3 입력 (Borrow considered)(X, Y, B0)과 2 출력 (차 : D, 자리빌림 : B1) • 진리표 반감산기(Half Subtractor : HS) 전감가산기(Full Subtractor : FS) • 반감산기 • 전감산기

컴퓨터의 논리 회로:부호 해독기(Decoder) • 디코더(Decoder) • n비트의 2진 입력을 받아 2n개의 출력 중 하나를 활성화 • 활용 : 메모리 칩 선택 신호, 명령어 해독과 제어 장치 등에 사용 • n×2n디코더 : n개의 입력과 2n개의 출력 • 2 × 4 디코더를 설계 • 1. 입출력 변수의 개수를 결정/변수를 할당 2 입력 (A, B), 4 출력(D0, D1, D2, D3) • 2. 진리표를 작성 • 3. 맵을 이용한 간소화 • 4. 논리회로 작성 2×4 디코더