Synchronous Counters Chapter 18

Synchronous Counters Chapter 18. Subject : Digital System Year : 2009. Overview. Up/ Down synchronous Counters Design of synchronous Counters Cascaded Counter Counter Decoding Application of Counter. Up/ Down synchronous Counters. Design of synchronous Counters.

Synchronous Counters Chapter 18

E N D

Presentation Transcript

Synchronous CountersChapter 18 Subject : Digital System Year : 2009

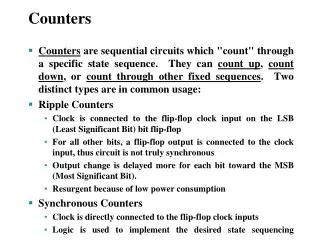

Overview • Up/ Down synchronous Counters • Design of synchronous Counters • Cascaded Counter • Counter Decoding • Application of Counter

Design of synchronous Counters • Step Procedure for seqeuantial circuit : • State Diagram • Next-State Table • Flip-Flop Transition Table • Karnaugh Maps • logic Expressions for Flip-Flop Inputs • Counter Implementation

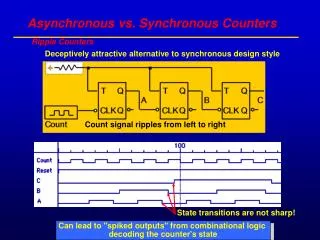

Cascaded Counter • Sebuah counter dapat dihubungkan dengan counter lain untuk memperoleh hasil yang lebih besar • Secara umum cascading dari sebuah counter berarti menghubungkan stage akhir output dari counter pertama kedalam input counter kedua.

Cascaded Counter • Pada gambar slide sebelumnya yang digunakan adalah 2 buah binary ripple counter, dari timing diagram terlihat bahwa state counter Q4 terjadi setiap 32 clock cycle, sehingga counter yang tercipta adalah modulus 32. • Ketika rangkaian yang digunakan adalah rangkaian synchronous counter diperlukan suatu control tambahan yaitu counter enable (CTEN) dan terminal count (TC) untuk membuat pembagian dari counter lebih besar. • Pada beberapa IC digital CTEN sering diberikan label G dan TC diberikan label ripplce clock output (RCO)

Cascaded counter • Cascade decade synchronous counter • Pada rangkaian diatas pin TC dari counter 1 dihubungkan ke pin CTEN counter 2, pada kondisi awal pin CTEN berada pada kondisi LOW, setelah counter 1 selesai menghitung maka pin tersebut akan HIGH dan counter 2 akan berpindah state • Secara umum counter 2 baru akan berpindah state apa bila counter 1 telah mencapai 10 cycle. Sehingga secara keseluruhan modulus dari counter 2 adalah 10x10 = 100 clock frequency

Counter decoding • Pada beberapa aplikasi terkadang perlu beberapa atau bahkan semua state dari counter di decodekan • Decode dari sebuah counter melibatkan beberapa gerbang atau bahkan penambahan decoder untuk menentukan kapan decoder berada pada state atau masuk kepada state tertentu. • Contoh pin terminal count (TC) pada cascade synchronous counter.

Counter decoding • Contoh kasus: Ada sebuah 3 bit counter, dan pada saat state nya berada pada kondisi 6(110b) ada sebuah keluaran pin yang mengeluarkan HIGH yang menandakan bahwa angka 6 telah tercapai. • Maka rangkaian penyelesaian untuk kasus tersebut adalah sebagai berikut:

Counter decoding • Rangkaian diatas dinamakan active-HIGHdecoding, apabila gerbang AND diganti dengan NAND maka rangkaian disebut active-LOW decoding. • Tugas: buatlah sebuah rangkaian dengan menggunakan 3 bit counter, dimana pada saat state berada pada posisi 2(010b) dan 7(111b) mengeluarkan output HIGH

Counter Application • Sebuah digital counter dapat digunakan untuk bermacam-macam aplikasi, beberapa rangkaian tersebut adalah: • Digital clock • Sensor ketersediaan tempat parkir • Parallel to serial data conversion (multiplexing)

Counter Application • Digital Clock:

Counter Application • Sensor ketersediaan tempat parkir: