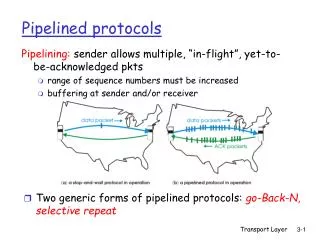

Control Hazards in Pipelined Implementations: Handling Techniques and Examples

This document outlines the challenges of control hazards in pipelined processor implementations. It discusses special cases, control dependencies, and the significance of branch mispredictions, providing examples including loops and return instructions. The document details how instructions can be affected by these hazards leading to incorrect execution. Techniques to handle mispredictions, such as using bubbles in the pipeline and managing instruction flows, are exemplified, with demo codes provided for practical understanding. Suggested readings for further learning are also included.

Control Hazards in Pipelined Implementations: Handling Techniques and Examples

E N D

Presentation Transcript

Outline • Handle Control Hazard • Special cases • Suggested Reading 4.5

Control Dependence • Example: loop: subl %edx, %ebx jne targ irmovl $10, %edx jmp loop targ: halt • The jne instruction create a control dependency • Which instruction will be executed?

Branch Misprediction Example • #demo-j.ys • 0x000: xorl %eax,%eax • 0x002: jne t # Not taken • 0x007: irmovl $1, %eax # Fall through • 0x00d: nop • 0x00e: nop • 0x00f: nop • 0x010: halt • 0x011: t: irmovl $3, %edx # Target (Should not execute) • 0x017: irmovl $4, %ecx # Should not execute • 0x01d: irmovl $5, %edx # Should not execute • Should only execute first 7 instructions

Select PC int F_predPC = [ f_icode in {IJXX, ICALL} : f_valC; 1: f_valP; ];

Branch Misprediction Trace 1 2 3 4 5 6 7 8 9 1: 0x000: xorl %eax,%eax 2: 0x002: jne T # Not taken 3: 0x00e: irmovl $2, %edx # T 4: 0x014: irmovl $3, %ebx # T+1 5: 0x007: irmovl $1, %eax # Fall Through F D E M W F D E M W F D E M W F D E M W F F D D E E M M W W Cycle 5 # demo-j.ys 0x000: xorl %eax,%eax 0x002: jne T# Not taken 0x007: irmovl $1, %eax 0x00d: halt 0x00e: T:irmovl $2, %edx 0x014: irmovl $3, %ebx 0x01a: halt Memory M_Cnd=0 M_valA=0x007 Excute e_valEf2 E_dstE=%edx Decode D D_valC=3 D_dstE=%ebx Incorrectly execute two instructions at branch target Fetch F f_valCf1 rBf%eax

Select PC int f_PC = [ #mispredicted branch. Fetch at incremented PC M_icode == IJXX && !M_Cnd : M_valA; #completion of RET instruciton W_icode == IRET : W_valM; #default: Use predicted value of PC 1: F_predPC ];

Return Example #demo-ret.ys 0x000: irmovl Stack,%esp # Intialize stack pointer 0x006: nop # Avoid hazard on %esp 0x007: nop 0x008: nop 0x009: call p # Procedure call 0x00e: irmovl $5,%esi # Return point 0x014: halt 0x020: .pos 0x20 0x020: p: nop # procedure 0x021: nop 0x022: nop 0x023: ret 0x024: irmovl $1,%eax # Should not be executed 0x02a: irmovl $2,%ecx # Should not be executed 0x030: irmovl $3,%edx # Should not be executed 0x036: irmovl $4,%ebx # Should not be executed 0x100: .pos 0x100 0x100: Stack: # Stack: Stack pointer • Require lots of nops to avoid data hazards

Incorrect Return Example 1 2 3 4 5 6 7 8 9 1: 0x023: ret 2: 0x024: irmovl $1,%eax #Oops 3: 0x02a: irmovl $2,%ecx #Oops 4: 0x030: irmovl $3,%edx #Oops 5: 0x00e: irmovl $5,%esi #Ret point F D E M W F D E M W F D E M W F D E M W F F D D E E M M W W Cycle 5 Write Back W_ValM=0x00e Memory Incorrectly execute 3 instructions following ret M_valE=1 M_dstE=%eax Excute e_valEf2 E_dstE=%ecx Decode D D_valC=3 D_dstE=%edx Fetch F f_valCf5 rBf%esi

Handling Misprediction # demo-j.ys 0x000: xorl %eax,%eax 0x002: jne T# Not taken 0x007: irmovl $1, %eax 0x00d: halt 0x00e: T:irmovl $2, %edx 0x014: irmovl $3, %ebx 0x01a: halt # demo-j2.ys 0x000: xorl %eax,%eax 0x002: jne T# Not taken 0x007: irmovl $1, %eax 0x00d: halt 0x00e: T:nop 0x00f: nop 0x010 irmovl $2, %edx 0x016: irmovl $3, %ebx 0x01c: halt

1 2 3 4 5 6 7 8 9 10 F F D D E E M M W W F F D D E E M M W W F D E M W F D E M W F F D D E E M M W W F F D D E E M M W W Handling Misprediction • #demo-j.ys • 1: 0x000: xorl %eax, %eax • 2: 0x002: jne T #Not Taken • 3: 0x00e: irmovl $2, %edx # T • 4: bubble • 5: 0x014: irmovl $3, %ebx # T+1 • 6: bubble • 7: 0x007: irmovl $1, %eax # Fall through • 8: 0x00d: halt • Predict branch as taken • Fetch 2 instructions at target • Cancel when mispredicted • Detect branch not-taken in execute stage • On following cycle, replace instructions in execute and decode by bubbles • No side effects have occurred yet

Detecting Mispredicted Branch Cnd icode M dstE dstM valE valA e_Cnd ALU ALU ALU CC CC fun. ALU ALU A B Execute E dstM srcA srcB icode ifun valC valA valB dstE

1 2 3 4 5 6 7 8 9 10 F F D D E E M M W W F F D D E E M M W W F D E M W F D E M W F F D D E E M M W W F F D D E E M M W W Control for Misprediction #demo-j.ys 1: 0x000: xorl %eax, %eax 2: 0x002: jne T #Not Taken 3: 0x00e: irmovl $2, %edx # T 4: bubble 5: 0x014: irmovl $3, %ebx # T+1 6: bubble 7: 0x007: irmovl $1, %eax # Fall through 8: 0x00d: halt

E_ icode W icode valE valM dstE dstM M icode Bch valE valA dstE dstM E_bubble Pipe E icode ifun valC valA valB dstE dstM srcA srcB control logic srcB srcA D_bubble D icode ifun rA rB valC valP F predPC

Return Example #demo-retB.ys 0x000: irmovl Stack,%esp # Intialize stack pointer 0x006: call p # Procedure call 0x00b: irmovl $5,%esi # Return point 0x011: halt 0x020: .pos 0x20 0x020: p: irmovl $-1,%edi # procedure 0x026: ret 0x027: irmovl $1,%eax # Should not be executed 0x02d: irmovl $2,%ecx # Should not be executed 0x033: irmovl $3,%edx # Should not be executed 0x039: irmovl $4,%ebx # Should not be executed 0x100: .pos 0x100 0x100: Stack: # Stack: Stack pointer • Previously executed three additional instructions

F D E M W F D E M W F D E M W F D E M W F F D D E E M M W W Correct Return Example 1 2 3 4 5 6 7 8 9 #demo_retb 1: 0x026: ret 2: bubble 3: bubble 4: bubble 5: 0x00b: irmovl $5, %esi #return • As ret passes through pipeline, stall at F stage • While in D, E, and M stage • fetch the same instruction after ret 3 times. • Inject bubble into D stage • Release stall when reach W stage Cycle 5 Write Back W_ValM=0x00b • • • Fetch F f_valCf5 rBf%esi

Detecting Return Cnd M icode valE valA dstE dstM e_Cnd ALU ALU ALU CC CC fun. ALU ALU A B Execute E icode ifun valC valA valB dstE dstM srcA srcB d_ srcA d_ srcB dstE dstM srcA srcB Fwd Sel +Fwd A B Decode M A B Register Register file file E D icode ifun rA rB valC valP

F D E M W F D E M W F D E M W F D E M W F F D D E E M M W W Control for Return 1 2 3 4 5 6 7 8 9 #demo_retb 1: 0x026: ret 2: bubble 3: bubble 4: bubble 5: 0x00b: irmovl $5, %esi #return

E_ icode D_ icode W icode valE valM dstE dstM M_ icode Cnd M icode valE valA dstE dstM Pipe E icode ifun valC valA valB dstE dstM srcA srcB control logic D_bubble D icode ifun rA rB valC valP F_stall F predPC

Control Cases • Detection • Action

E_ icode d_ srcB d_ srcA D_ icode W icode valE valM dstE dstM M_ icode M icode Cnd valE valA dstE dstM e_Cnd CC CC E_ dstM E_bubble Pipe E icode ifun valC valA valB dstE dstM srcA srcB control logic srcB srcA D_bubble D icode ifun rA rB valC valP D_stall F_stall F predPC

Implementing Pipeline Control • Combinational logic generates pipeline control signals • Action occurs at start of following cycle

Initial Version of Pipeline Control bool F_stall = # Conditions for a load/use hazard E_icode in { IMRMOVL, IPOPL } && E_dstM in { d_srcA, d_srcB } || # Stalling at fetch while ret passes through pipeline IRET in { D_icode, E_icode, M_icode }; bool D_stall = # Conditions for a load/use hazard E_icode in { IMRMOVL, IPOPL } && E_dstM in { d_srcA, d_srcB };

Initial Version of Pipeline Control bool D_bubble = # Mispredicted branch (E_icode == IJXX && !e_Bch) || # Stalling at fetch while ret passes through pipeline IRET in { D_icode, E_icode, M_icode }; bool E_bubble = # Mispredicted branch (E_icode == IJXX && !e_Bch) || # Load/use hazard E_icode in { IMRMOVL, IPOPL } && E_dstM in { d_srcA, d_srcB};

1 1 1 2 2 2 3 3 3 Load/use Mispredict Mispredict ret ret ret ret ret ret ret ret ret ret ret ret M M M M M M M M M M M M Load bubble bubble bubble JXX JXX ret ret ret E E E E E E E E E E E E Use bubble bubble bubble bubble bubble bubble ret ret ret D D D D D D D D D D D D Combination A Combination B Control Combinations • Special cases that can arise on same clock cycle • Combination A • Not-taken branch • ret instruction at branch target • Combination B • Instruction that reads from memory to %esp • Followed by ret instruction

1 ret M E ret D 1 1 Mispredict Mispredict ret ret M M M M JXX JXX E E E E ret ret D D D D Combination A Control Combination A PC Instruction PC PC memory increment memory f_PC Fetch M_ valA Select PC W_ valM F predPC

Control Combination A • Should handle as mispredicted branch • Stalls F pipeline register • But PC selection logic will be using M_valA anyhow

Control Combination B Load/use ret • Would attempt to bubble and stall pipeline register D • Signaled by processor as pipeline error M M M M Load E E E E ret Use ret ret D D D D Combination B

Handling Control Combination B • Load/use hazard should get priority • ret instruction should be held in decode stage for additional cycle

Corrected Pipeline Control Logic bool D_bubble = # Mispredicted branch (E_icode == IJXX && !e_Cnd) || # Stalling at fetch while ret passes through pipeline IRET in { D_icode, E_icode, M_icode } # but not condition for a load/use hazard && !(E_icode in { IMRMOVL, IPOPL } && E_dstM in { d_srcA, d_srcB });

Pipeline Summary • Data Hazards • Most handled by forwarding • No performance penalty • Load/use hazard requires one cycle stall • Control Hazards • Cancel instructions when detect mispredicted branch • Two clock cycles wasted • Stall fetch stage while ret passes through pipeline • Three clock cycles wasted

Pipeline Summary • Control Combinations • Must analyze carefully • First version had subtle bug • Only arises with unusual instruction combination