Pipelined Datapath

Pipelined Datapath. Lecture notes from MKP, H. H. Lee and S. Yalamanchili. Reading. Sections 4.5 – 4.9. Pipeline Performance. Assume time for stages is 100ps for register read or write 200ps for other stages Compare pipelined datapath with single-cycle datapath. Pipeline Performance.

Pipelined Datapath

E N D

Presentation Transcript

Pipelined Datapath Lecture notes from MKP, H. H. Lee and S. Yalamanchili

Reading • Sections 4.5 – 4.9

Pipeline Performance • Assume time for stages is • 100ps for register read or write • 200ps for other stages • Compare pipelined datapath with single-cycle datapath

Pipeline Performance Single-cycle (Tc= 800ps) Pipelined (Tc= 200ps)

Pipeline Speedup • If all stages are balanced • i.e., all take the same time • If not balanced, speedup is less • Speedup due to increased throughput • Latency (time for each instruction) does not decrease

Basic Idea All instructions are 32-bits Few & regular instruction formats Alignment of memory operands

Pipelining • What makes it easy • All instructions are the same length • Simple instruction formats • Memory operands appear only in loads and stores • What makes it hard? • structural hazards: suppose we had only one memory • control hazards: need to worry about branch instructions • data hazards: an instruction depends on a previous instruction • What really makes it hard: • exception handling • trying to improve performance with out-of-order execution, etc.

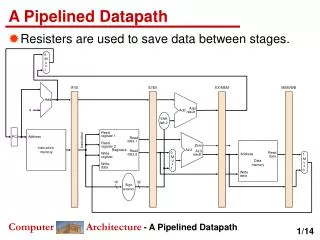

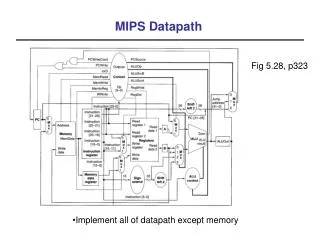

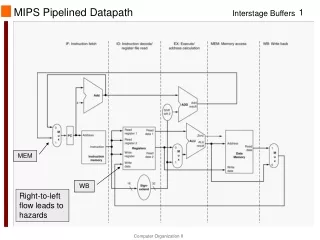

Pipeline registers • Need registers between stages • To hold information produced in previous cycle Pipeline stage execution time

MEM IF ID EX WB add Graphically Representing Pipelines 2 4 6 8 10 Time lw MEM IF ID EX WB • Shading indicates the unit is being used by the instruction • Shading on the right half of the register file (ID or WB) or memory means the element is being read in that stage • Shading on the left half means the element is being written in that stage

Graphically Representing Pipelines • Can help with answering questions like: • how many cycles does it take to execute this code? • what is the ALU doing during cycle 4? • use this representation to help understand datapaths T i m e ( i n c l o c k c y c l e s ) P r o g r a m C C 1 C C 2 C C 3 C C 4 C C 5 C C 6 e x e c u t i o n o r d e r ( i n i n s t r u c t i o n s ) l w $ 1 0 , 2 0 ( $ 1 ) I M R e g A L U D M R e g s u b $ 1 1 , $ 2 , $ 3 I M R e g D M R e g A L U

MEM MEM MEM IF IF IF ID ID ID EX EX EX WB WB WB Structural Hazard 2 4 6 8 10 Time lw MEM IF ID EX WB add sub add Need to separate instruction and data memory

IF for Load, Store, … Pipeline stage execution time

ID for Load, Store, … Pipeline stage execution time

EX for Load Pipeline stage execution time

MEM for Load Pipeline stage execution time

WB for Load Wrongregisternumber

Corrected Datapath for Load Pipeline stage execution time

EX for Store Pipeline stage execution time

MEM for Store Pipeline stage execution time

WB for Store Pipeline stage execution time

Pipelining Example add $14, $5, $6 lw $13, 24($1) add $12, $3, $4 sub $11, $2, $3 lw $10, 20($1) Note what is happening in the register file 0 M u x 1 I F / I D I D / E X E X / M E M M E M / W B A d d A d d 4 A d d r e s u l t S h i f t l e f t 2 R e a d n o r e g i s t e r 1 i A d d r e s s P C t R e a d c u d a t a 1 r t R e a d s Z e r o n r e g i s t e r 2 I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e A d d r e s s d a t a 2 1 r e s u l t d a t a r e g i s t e r M M u D a t a u W r i t e x m e m o r y x d a t a 1 0 W r i t e d a t a 1 6 3 2 S i g n e x t e n d I n s t r u c t i o n 0 [ 2 0 – 1 6 ] M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 Pipeline stage execution time R e g D s t

Pipelined Control • Control signals derived from instruction • As in single-cycle implementation • Pass control signals along like data

IF: lw $10, 9($1) P C S r c I D / E X 0 M W B u E X / M E M x 1 C o n t r o l M W B M E M / W B E X M W B I F / I D A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: sub $11, $2, $3 ID: lw $10, 9($1) P C S r c I D / E X 0 11 M W B u E X / M E M “lw” x 010 1 C o n t r o l M W B M E M / W B 0001 E X M W B I F / I D A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: and $12, $4, $5 ID: sub $11, $2, $3 EX: lw $10, 9($1) P C S r c I D / E X 0 11 10 M W B u E X / M E M “sub” x 010 000 1 C o n t r o l M W B 0 M E M / W B 1100 00 E X M W B I F / I D 1 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: or $13, $6, $7 ID: and $12, $4, $5 EX: sub $11, $2, $3 MEM: lw $10, 9($1) P C S r c I D / E X 0 10 10 M W B u E X / M E M “and” x 000 000 11 1 C o n t r o l M W B 0 1 M E M / W B 1100 1 10 E X M W B 0 I F / I D 0 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: add $14, $8, $9 ID: or $13, $6, $7 EX: and $12, $4, $5 MEM: sub $11, .. WB: lw $10, 9($1) P C S r c I D / E X 0 10 10 M W B u E X / M E M “or” x 000 000 10 1 C o n t r o l M W B 0 1 1 M E M / W B 1100 0 10 E X M W B 0 I F / I D 0 1 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: xxxx ID: add $14, $8, $9 EX: or $13, $6, $7 MEM: and $12… WB: sub $11, .. P C S r c I D / E X 0 10 10 M W B u E X / M E M “add” x 000 000 10 1 C o n t r o l M W B 0 1 1 M E M / W B 1100 0 10 E X M W B 0 I F / I D 0 0 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: xxxx ID: xxxx EX: add $14, $8, $9 MEM: or $13, .. WB: and $12… P C S r c 0 10 M I D / E X u E X / M E M x 000 10 W B 1 C o n t r o l W B 0 1 1 M E M / W B M 0 10 M W B 0 I F / I D 0 0 E X A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control

IF: xxxx ID: xxxx EX: xxxx MEM: add $14, .. P C S r c I D / E X 0 M W B u E X / M E M x 10 1 M C o n t r o l W B 0 1 M E M / W B 0 E X M W B 0 I F / I D 0 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control WB: or $13…

P C S r c I D / E X 0 M W B u E X / M E M x 1 M C o n t r o l W B 1 M E M / W B E X M W B I F / I D 0 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Datapath with Control IF: xxxx ID: xxxx EX: xxxx MEM: xxxx WB: add $14..

Data Hazards • An instruction depends on completion of data access by a previous instruction • add $s0, $t0, $t1sub $t2, $s0, $t3

Dependencies • Problem with starting next instruction before first is finished • dependencies that “go backward in time” are data hazards

Software Solution • Have compiler guarantee no hazards • Where do we insert the “nops” ? sub $2, $1, $3 and $12, $2, $5 or $13, $6, $2 add $14, $2, $2 sw $15, 100($2) • Problem: this really slows us down!

A Better Solution • Consider this sequence: sub $2, $1,$3and $12,$2,$5or $13,$6,$2add $14,$2,$2sw $15,100($2) • We can resolve hazards with forwarding • How do we detect when to forward?

Dependencies & Forwarding Do not wait for results to be written to the register file – find them in the pipeline forward to ALU

IF: add $14, $8, $9 ID: or $13, $6, $7 EX: and$6, $4, $5 MEM: sub $11, .. WB: lw $10, 9($1) P C S r c I D / E X 0 10 10 M W B u E X / M E M “or” x 000 000 10 1 C o n t r o l M W B 0 1 1 M E M / W B 1100 0 10 E X M W B 0 I F / I D 0 1 A d d A d d 4 A d d r e s u l t e t i r B r a n c h W S h i f t g e l e f t 2 e t i R r A L U S r c W m g R e a d n e e o i r e g i s t e r 1 M R A d d r e s s P C t R e a d c o t u d a t a 1 r m t R e a d s e Z e r o n r e g i s t e r 2 M I I n s t r u c t i o n R e g i s t e r s A L U R e a d A L U m e m o r y 0 R e a d W r i t e d a t a 2 A d d r e s s r e s u l t 1 d a t a r e g i s t e r M M D a t a u u m e m o r y W r i t e x x d a t a 1 0 W r i t e d a t a I n s t r u c t i o n 1 6 3 2 6 [ 1 5 – 0 ] S i g n A L U M e m R e a d e x t e n d c o n t r o l I n s t r u c t i o n [ 2 0 – 1 6 ] 0 A L U O p M u I n s t r u c t i o n x [ 1 5 – 1 1 ] 1 R e g D s t Forwarding

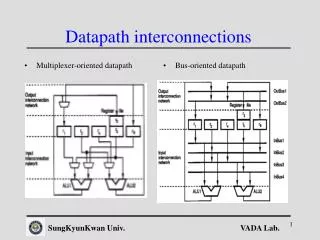

Forwarding (simplified) ID/EX EX/MEM MEM/WB Register File Data Memory ALU MUX

MUX MUX Forwarding (from EX/MEM) ID/EX EX/MEM MEM/WB Register File Data Memory ALU MUX

MUX MUX Forwarding (from MEM/WB) ID/EX EX/MEM MEM/WB Register File Data Memory ALU MUX

MUX MUX Forwarding (operand selection) ID/EX EX/MEM MEM/WB Register File Data Memory ALU MUX Forwarding Unit

MUX MUX MUX Forwarding (operand propagation) ID/EX EX/MEM MEM/WB Register File Data Memory ALU MUX Rd Rt EX/MEM Rd Forwarding Unit Rt Rs MEM/WB Rd Combinational Logic!

Detecting the Need to Forward • Pass register numbers along pipeline • e.g., ID/EX.RegisterRs = register number for Rssitting in ID/EX pipeline register • ALU operand register numbers in EX stage are given by • ID/EX.RegisterRs, ID/EX.RegisterRt • Data hazards when 1a. EX/MEM.RegisterRd = ID/EX.RegisterRs 1b. EX/MEM.RegisterRd = ID/EX.RegisterRt 2a. MEM/WB.RegisterRd = ID/EX.RegisterRs 2b. MEM/WB.RegisterRd = ID/EX.RegisterRt Fwd fromEX/MEMpipeline reg Fwd fromMEM/WBpipeline reg

Detecting the Need to Forward • But only if forwarding instruction will write to a register! • EX/MEM.RegWrite, MEM/WB.RegWrite • And only if Rd for that instruction is not $zero • EX/MEM.RegisterRd ≠ 0,MEM/WB.RegisterRd ≠ 0

Forwarding Conditions • EX hazard • if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRs))ForwardA = 10 • if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRt))ForwardB = 10 • MEM hazard • if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0) and (MEM/WB.RegisterRd = ID/EX.RegisterRs))ForwardA = 01 • if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0) and (MEM/WB.RegisterRd = ID/EX.RegisterRt))ForwardB = 01

Double Data Hazard • Consider the sequence: add $1,$1,$2add $1,$1,$3add $1,$1,$4 • Both hazards occur • Want to use the most recent • Revise MEM hazard condition • Only forward if EX hazard condition isn’t true

Revised Forwarding Condition • MEM hazard • if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)and not (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRs)) and (MEM/WB.RegisterRd = ID/EX.RegisterRs))ForwardA = 01 • if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)and not (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRt)) and (MEM/WB.RegisterRd = ID/EX.RegisterRt))ForwardB = 01 • Checking precedence of EX hazard