A Pipelined Datapath

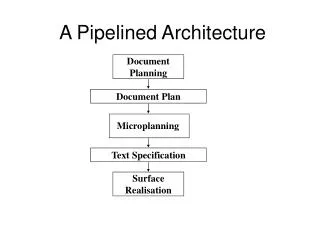

A Pipelined Datapath. Resisters are used to save data between stages. 1/14. Corrected Datapath. The Write Register in the IF/ID register is from the wrong instruction. The Write Register is passed through the pipeline and forwarded to the Register File (RF) from the MEM/WB register. 2/14.

A Pipelined Datapath

E N D

Presentation Transcript

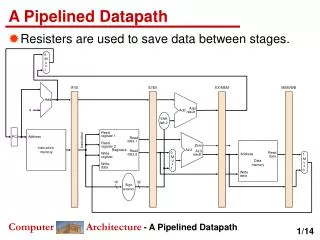

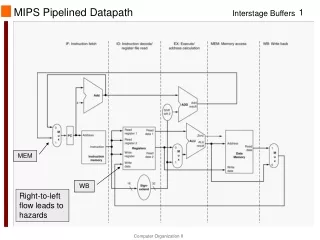

A Pipelined Datapath • Resisters are used to save data between stages. Computer Architecture- A Pipelined Datapath 1/14

Corrected Datapath • The Write Register in the IF/ID register is from the wrong instruction. • The Write Register is passed through the pipeline and forwarded to the Register File (RF) from the MEM/WB register. Computer Architecture- A Pipelined Datapath 2/14

Instructions in the Pipeline (Clock 2) sub $11,$2,$3 lw $10,20($1) Computer Architecture- A Pipelined Datapath 3/14

Instructions in the Pipeline (Clock 4) sub $11,$2,$3 lw $10,20($1) Computer Architecture- A Pipelined Datapath 4/14

Instructions in the Pipeline (Clock 5) sub $11,$2,$3 lw $10,20($1) Computer Architecture- A Pipelined Datapath 5/14

Pipelined Control • Problem: Control lines are defined in the IF stage. • Example: In the WB stage MemtoReg and RegWrite are opcode dependent. • Solution: Pass the control lines through the pipeline. Computer Architecture- A Pipelined Datapath 6/14

Pipeline Datapath with Control Computer Architecture- A Pipelined Datapath

Data Dependencies • Backward lines cause data hazards: sub $2,$1,$3 and $12,$2,$5 or $13,$6,$2 add $14,$2,$2 sw $15,100($2) Computer Architecture- A Pipelined Datapath 8/14

2 Easy Solutions • The RF is written into in the 1st half of the cycle and read from in the 2nd half of the cycle. • Thus the data written is the data read. The add instruction isn’t a hazard. • Disallow data hazards byadding aninstruction called nop (no operation). • Now there aren’t anydata hazards. sub $2,$1,$3 nop nop and $12,$2,$5 or $13,$6,$2 add $14,$2,$2 sw $15,100($2) Computer Architecture- A Pipelined Datapath 9/14

Detecting And Forwarding • Easy. Each pipeline register contains the Rs, Rt, and Rd of the current instruction. • If one of the next equalities is true there is a hazard: • EX/MEM.Rd == ID/EX.Rs • EX/MEM.Rd == ID/EX.Rt • MEM/WB.Rd == ID/EX.Rs • MEM/WB.Rd == ID/EX.Rs • A unit called the Forwarding Unit decides if there is a hazard and solves it by using forwarding. • The values are directed from the EX/MEM and MEM/WB registers to the ALU. Computer Architecture- A Pipelined Datapath 10/14

The Forwarding Unit Computer Architecture- A Pipelined Datapath 11/14

Data Hazards and Stalls • Sometimes Forwarding doesn’t work (load-use data hazard): lw $2,20($1) and $4,$2,$5 or $8,$2,$6 add $9,$4,$2 slt $1,$6,$7 Computer Architecture- A Pipelined Datapath 12/14

Inserting a Bubble • The EX,MEM, and WB control fields of the ID/EX register are set to 0. The PC and IF/ID register aren’t updated. This causes the and & or instructions to repeat cycle 3 during cycle 4. Computer Architecture- A Pipelined Datapath 13/14

Hazard Detection Unit The hardware doesn’t depend on the compiler to detect and eliminate data hazards. A smart compiler will help in order to achieve better performance. Computer Architecture- A Pipelined Datapath 14/14