Exploring Mealy and Moore Finite State Machines in VHDL for Sequence Detection

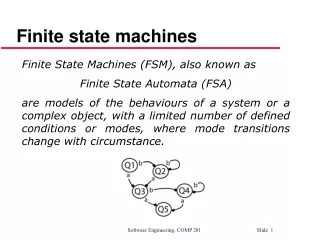

This document delves into the analysis and implementation of Mealy and Moore finite state machines (FSMs) using VHDL. It includes a detailed examination of state transitions, input sequences, and output generation, focusing on detecting the binary sequence "1101". The state diagrams and sample VHDL code illustrate the operation of the FSMs, showcasing the differences in their response to input changes. Additionally, discussions on combinational networks and sequential networks provide a comprehensive understanding of FSM design and functionality in digital systems.

Exploring Mealy and Moore Finite State Machines in VHDL for Sequence Detection

E N D

Presentation Transcript

Finite State Machines Discussion D7.1 Mealy and Moore Machines

init Combinational Network s(t+1) s(t) State Register next state present state x(t) present input present output clk z(t) Canonical Sequential Network

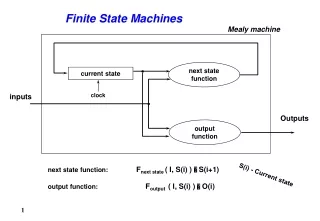

init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input clk Mealy Machine

init C2 C1 z(t) s(t+1) State Register next state s(t) present state x(t) present input clk Moore Machine

VHDLCanonical Sequential Network init Combinational Network s(t+1) s(t) State Register next state present state x(t) present input process(clk, init) present output clk z(t) process(present_state, x)

VHDLMealy Machine process(present_state, x) init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input process(present_state, x) clk process(clk, init)

VHDLMoore Machine init C2 C1 z(t) s(t+1) State Register next state s(t) present state x(t) present input process(present_state, x) process(present_state) clk process(clk, init)

ExampleDetect input sequence 1101 fsm din clk dout clr din dout 1 0 1 1 0 1 1 0 1 0 0 1 1 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0

0 1 1 0 0 1 CLR 0 1 0 1 Use State DiagramDetect input sequence 1101 S1 0 S0 0 S11 0 S1101 1 S110 0

fsm.vhd fsm din clk dout clr

clr dout din fsm.vhd

clr dout din fsm.vhd

S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1 fsm.vhd

fsm.vhd S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1

clr dout din fsm.vhd

fsmx.vhd LD(0) LD(1) din fsm dout clr LD(7) BTN(3) clk BTN(1) bn clk_pulse BTN(0) fsmx cclk mclk clkdiv

fsmx.vhd entity fsmx is port( mclk : in STD_LOGIC; SW : in STD_LOGIC_VECTOR(7 downto 0); BTN : in STD_LOGIC_VECTOR(3 downto 0); LD : out STD_LOGIC_VECTOR(7 downto 0); AtoG : out STD_LOGIC_VECTOR(6 downto 0); dp : out STD_LOGIC; AN : out STD_LOGIC_VECTOR(3 downto 0) ); end fsmx;

fsmx.vhd component clock_pulse port( inp : in std_logic; cclk : in std_logic; clr : in std_logic; outp : out std_logic); end component; signal clr, clk, cclk, bn: std_logic; signal clkdiv: std_logic_vector(23 downto 0);

fsmx.vhd bn <= BTN(1) or BTN(0); clr <= BTN(3); U0: clk_pulse port map (inp => bn, cclk => cclk, clr =>clr, clk => clk); U1: fsm port map (clr =>clr, clk => clk, din => BTN(1), dout => LD(7)); LD(0) <= BTN(0); LD(1) <= BTN(1);