Understanding Basic Instruction Fetching in CSE241

DESCRIPTION

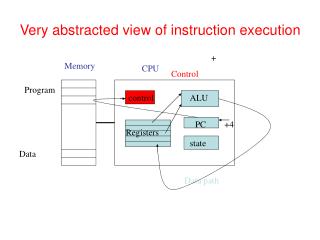

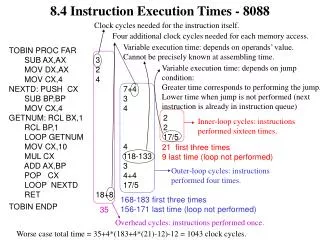

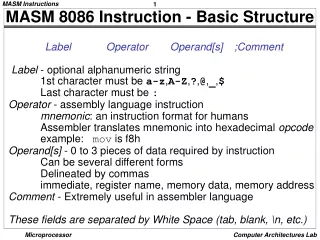

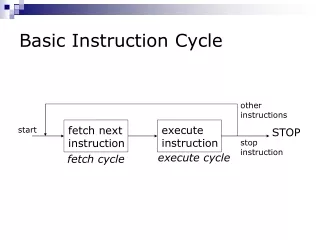

This content focuses on the fetch cycle in computer architecture, particularly within the CSE241 framework. The description of each step reveals how the instruction is processed: loading the Program Counter (PC) to the Memory Address Register (MAR), reading data into the Memory Data Register (MDR), and transferring instruction data into the Instruction Register (IR). With an emphasis on parallel execution, the fetch cycle highlights the importance of efficient data handling and flow control in microprocessors, underpinning the mechanics of instruction execution.

1 / 29

Télécharger la présentation

Understanding Basic Instruction Fetching in CSE241

An Image/Link below is provided (as is) to download presentation

Download Policy: Content on the Website is provided to you AS IS for your information and personal use and may not be sold / licensed / shared on other websites without getting consent from its author.

Content is provided to you AS IS for your information and personal use only.

Download presentation by click this link.

While downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server.

During download, if you can't get a presentation, the file might be deleted by the publisher.

E N D

Presentation Transcript

More Related