Advanced XOR Applications in Digital Logic: Combinational Circuit Design and Implementation

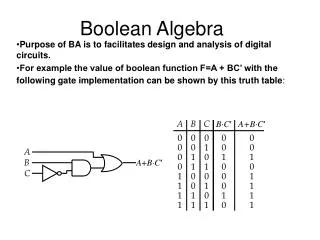

This project focuses on the analysis and design of combinational circuits, emphasizing the use of Exclusive-OR (XOR) and its equivalence (XNOR) in Boolean algebra. Students will determine input/output relationships, create Boolean equations, and generate truth tables. The design will be implemented on an FPGA using Xilinx ISE Design Suite, including schematic capture and VHDL coding. The project culminates in generating a programming file to configure the FPGA and test the circuit operation. Teams of two will compile detailed project reports documenting all findings.

Advanced XOR Applications in Digital Logic: Combinational Circuit Design and Implementation

E N D

Presentation Transcript

Boolean Algebra (Continued) ELEC 311 Digital Logic and Circuits Dr. Ron Hayne Images Courtesy of Cengage Learning

Exclusive-OR (XOR) 311_03

XOR Theorems 311_03

Equivalence 311_03

Equivalence (XNOR) 311_03

Project 1 • Combinational Circuit Analysis • Determine input/output relationship of function • Boolean Equation • Truth Table • Implement logic circuit with FPGA • Schematic capture design tools • Test circuit to verify operation • Project Report • Teams of 2 persons 311_03

Xilinx ISE Design Suite • Enter description of logic circuit • Schematic editor • VHDL • Use a logic synthesizer to generate a netlist • Use implementation tools to map logic gates and interconnections into the FPGA • Generate a bitstream programming file • Configure device • Download the bitstream to the FPGA chip 311_03

Schematic or 311_03

File → New Project Project Name Demo1 Project Location C:\xxx\xxx Top-Level Module Type Schematic Device Family Spartan3E Device XC3S100E Package TQ144 (BASYS) CP132 (BASYS 2) Speed Grade -5 New Project 311_03

Project → New Source Schematic Demo1 Schematic Editor Symbols Category list Symbol list Drawing area Tools Add wire Add I/O marker New Source 311_03

add wire add I/O marker 311_03

Categories Logic Symbols and2 and3 inv or2 Add wires Point to point Stubs I/O Markers Input marker Output marker Rename Port Demo1 Schematic 311_03

FPGA LEDs Switches 311_03

FPGA Pins 311_03

Constrain the Design • User Constraints → I/O Pin Planning – Pre-Synthesis • Implementation Constraints File • Demo1.ucf • PlanAhead • I/O Ports • Site 311_03

Synthesize & Implement • Synthesize Design • Implement Design • Generate Programming File 311_03

BASYS Configuration Set to ROM 311_03

Configure Device • Configure Device (Adept) • Initialize Chain • XCF02S (PROM) • demo1.bit • Program • Cycle Power (Reset) 311_03

Test the Design XY F 1 X Y Z 0 311_03

Project Report • Cover Sheet • Project Name/Number • Authors • Professor’s Initials • Objectives • Discussion • Boolean Equation • Truth Table • Circuit Schematic • Conclusion • Test Results 311_03