Preshower FE Board design

Preshower FE Board design. R. Bonnefoy, G. Bohner, C. Cârloganu, E. Conte, R. Cornat, E. Delage, J. Lecoq M-L. Mercier, P. Perret cornat@clermont.in2p3.fr. III. Overview : FE board. TRIG : APA450 2*64 trigger bits SPD multiplicity and 2x2 cluster. II. 8 AX1000 (data proc. + L0).

Preshower FE Board design

E N D

Presentation Transcript

Preshower FE Board design R. Bonnefoy, G. Bohner, C. Cârloganu, E. Conte, R. Cornat, E. Delage, J. Lecoq M-L. Mercier, P. Perret cornat@clermont.in2p3.fr

III Overview : FE board TRIG : APA450 2*64 trigger bits SPD multiplicity and 2x2 cluster II 8 AX1000 (data proc. + L0) 64 ADC + Op. Amp Each AX receives 8 SPD bits x 64 DAQ & TTC : SEQ (LAL) VFE clk & rst Clock distribution Power & delatchers I IV ECS : GLUE (LAL)

TRIG TOP/BOT neighbours 2*16b serial LVDS on cables PCB & I/Os TRIG RIGHT/LEFT neigh. 2*18 LVDS on backplane 2x2 cluster to VALIDATION 2*13b serial LVDS on cables 20 bits to DAQ Serial LVDS on backplane • 12 layers, class 6 • LAL backplane & crate • 1 test support on one FE_PGA • Connector for external USB/I2C generator (needs GLUE modifications) 64 analogue inputs RJ45 connectors Ethernet CAT6 cable SPD multiplicity 21b serial LVDS on backplane 2 ECAL @+BXID 2*21 bits serial LVDS on cables 2 clk & 2 rst to VFE Differential ECL on cables 64 SPD inputs Serial LVDS on cables

On board data flow • Point to point parallel links only • Easy to test with injection and acquisitions RAM in FE, TRIG and SEQ pgas • Production • Commissioning • JTAG scan path available

Tests connectors • JTAG • Program (APA) • Test (externally cabled JTAG chain thanks to individual connectors) • Tests (SiliconExplorer) • Debugging steps

TTC & clocksECS L0 Ch B • I2C : point to point from GLUE to chips • Clocks : LVDS • LAL delay chips • Converted to CMOS close to chips I2C RST

ECS • Same as ECAL FE board (SPECS, CROC, GLUE) • LPC made I2C interface • Used on L0DU & VALIDATION board • ACK check • 8b reg. addressed according to their position into the frame • Reg. bank loaded in 1 frame (SW opt.)

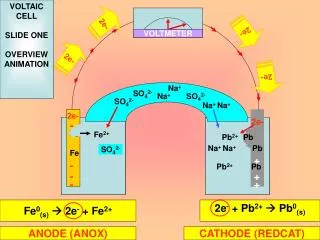

Power supply • Use of -3.3 and 3.3 V only • Not compatible with ECAL/HCAL FE boards • -3.3V, 1.5 and 2.5 V made with LHC regulators • SEL sensitive components are protected with self switch-off current limiters • Switch with feed back acting as « delatchers » • Partitions of components

Switch characteristics • Current limiter • (2A : MAX869, 1.2A : MAX890, • 0.5A : MAX891,…) • 2.7 to 5.5 V • Switch resistance : 90 m typ.@3V • Programmable current limit (external resistor) • Minimum limit is 0.2*Imax (240 mA for MAX890) • Fault indicator • Enable input (forced switch off is possible) • Thermal shutdown • MAX869L was tested at GANIL by LAL • SN74LVC10 tested by ATLAS 74LVC010 Test circuit

FE pga AX1000 Digital processing

FEpga • AX1000 pga : digital processing & L0/DAQ • 8b SPD data • Pipe-lines (ECAL vs PS, SPD vs PS) • Tests RAMS (injection & acquisition) • ECS : 3 banks of resp. 10, 2*34 8b reg. + RAMs • LAL L0 readout • ECS interfaces are LPC made • Worst case : 56 MHz • Best case : slack > 300 ps • Cells : 53%, RAM : 70%, IO : 50% • Back annotated simulations • Entry point : I2C

Digital processing • Offset [0..255] • Gain = 1+ G/512, G [0..255] • Alpha = A/512, A [0..255] • Trigger threshold [0..255] 8 bits parameters Optimized operators sizes 4 pipe-line steps

Error flags ALGOETHAMMING Load command bits and data dispatching TV1 Flags_register Muxdreg ECS data PIPELINEBYPASS Tmr_registerr TV1 Flags_register TVERR Tmr_tv protocol TV1 Flags_register ECS1 Psfeeecs_protocol_34_err Error bits Error bit bypass OR Pipeline length Algo. parameters Trig_out PHY I2C1 I2csl7b_2 PIPELINE1 pipelineced ALGO1 Psdataalgo_bp Data_out STOCKAGE16B4V Hamming_partiel4voies4a16 Trig_out PIPELINE2 pipelineced ALGO2 Psdataalgo_bp Data_out Communication bus (i2c) DECODEUR Hamming_22_16_3_decoder Trig_out PIPELINE3 pipelineced ALGO3 Psdataalgo_bp Data_out 40 MHz data RAM+MUX Trig_out PIPELINE4 pipelineced ALGO4 Psdataalgo_bp Data_out 40 MHz data General architecture ACQ RAM

22 bits words 16 data bits 5 hamming bits 1 global parity bit Loaded by 8 bits slices from I2C 1 bit error correction 2 bits error detection Decoder shared among 12 22b registers Cyclic check and correction using a counter 22 22 22 22 gain alpha et threshold offset 22 22 22 tmr counter mux 2 errcod Hamming decoder Bits Mapping Bits Mapping Bits Mapping 8 8 8 8 8 8 gain1 gain2 offset1 offset2 alpha Half channel synchronization Half channel synchronization synchro 8 8 threshold gain offset HammingFor parameters registers load_ecs

L0 trigger • Link ECAL to PS/SPD • Trigger data = 1b/ch

Overview : trigger functions • Interconnection between : • SPD and PS (boards corresponding to the same cells) : 24m serial LVDS • Adjacent PS board (T/B : lvcmos 40MHz, R/L : serial LVDS) • ECAL and PS (boards corresponding to the same cells) : serial LVDS • PS and ECAL validation board : serial LVDS • PS and SPD control board (multiplicity) : serial LVDS • Synchronization : compensate latencies • Cells mapping issue : geographic algorithms • 2x2 cluster search algorithm for SPD an PS trigger bits

Trigger task • Two cluster addresses sent by ECAL • One per half PS FE Board • SPD data deserilization • Received in FE PGAs : sent to DAQ • Centralized into TRIG PGA • Neighbours algorithm • Transmission between boards • Simple multiplexor… • Need one Tclk • Algorithm validated (Q1’01 prototype) • SPD Multiplicity • Adder tree • Data synchronization • Many pipe-lines…

Timing model 6 pipe-line length to set

P&R results • Worst case : 52 MHz • Best case : slack > 55 ps • Cells : 38%, RAM : 69%, IO : 90% • P&R : routing resources usage close to a limit (uncertain P&R result) • Routing is critical • Frozen pin positions (PCB) • Large buses (128b typ) to connect mapping steps, pipe-lines, RAMS, etc… • 5% more nets lead to 20% loss in max. frequency • But : current version is ok and seem to be final

Logical clock tree • Delay chips allow to set • VFE (start of analogue integration time) • VFERST (phase of VFE rst signal) • ADC (analogue signal sampling time) • ADC’ (ADC data sampling time into FE_PGAs) • Sampling times of serial LVDS data (SPD, ECAL, TOP) • Clk taken from the backplane • No LVDS RT fan-out found… • Delay chips and LV048 • Multidrop LVDS (Up to 2*4 LVDS buffers per branch) • Tree trunk and branches are LVDS • Tree leaves are LVTTL

SCL ECAL Clock inside PGAs • Clock regions to optimize best case timing slack (TRIG) • Use of PLL • Dedicated pins to use hardwired clock trees

Clock model Fe_PGA P0

Clock distribution (schematics) Global clk ADC in FEpga 8 FE 1 TRIG 1 SEQ 1 GLUE 4 serializers SPD in FEpga Inputs of TRIGpga VFE 4*16 ADCs

Radiation test of the Preshower electronics • Have been tested at Ganil in April 2003 • Front-End electronic • ADC (AD9203): 4 chips • Operational Amplifier (AD8132): 4 chips • Very-Front-End electronic • New version of the ASIC integrator: 2 chips with 1 complete channel each • Active PMT Base (AB): 2 basis with 2 HV transistors each • No cumulated dose effects • 26 krad for AB, ASIC and OA • 52 krad for ADC • Some SEL observed for ADC • Not destructive • The 4 ADC have been tested getting back to laboratory • They all work perfectly • Current in the ADC increased “only” by a factor 3 to 4 • Holding the power supply voltage in the required range • Estimation : 10 SEL per year • Use of delatchers • No SEL for AB, ASIC and OA

Triple voting • Antifuse PGA (FE), RT flash PGA (TRIG, SEQ, GLUE) • Triple voting technique : • Used on control bits and FSM state register • Used on RAM address counters • Hamming counters developed (HDL) • Error bits are summarized (logical OR)

22 bits words 16 data bits 5 hamming bits 1 global parity bit 1 bit error correction 2 bits error detection Decoder can be shared with many registers Cyclic check and correction using a counter Saves a lot of flip-flops Needs combinational logic Used for alg. param. reg. Synthesis results (4 FE channels) : EDAC Hamming coding

Current prototype • Main current switch needs more studies • ECS error rate too high • Errors seen on SPECS signals before CROC • PCB & PGA intensely tested

Q2’01 Analogue receiver & ADC

Constraints 1 cm height per channel 64 channels/32 cm EMC Noise σ=0,8 mV lowered to 0,4 mV PCB hierarchical block CMS 0805 AD9203 Compact placement Ground plane Signal diff. pairs Diff. clock Prototype

Q4’03 New analogue module • Refined component placement • Compatible for both ADC multiplexing and direct connection to Fe_PGA Optimized differential signal traces