Teaching Advanced Test Issues in Digital Electronics

E N D

Presentation Transcript

Teaching Advanced Test Issues in Digital Electronics ITHET 6th Annual International Conference Juan Dolio, Dominican Republic, July 9, 2005 E.Orasson, J.Raik, R. Ubar TU Tallinn, ESTONIA H.-D.Wuttke TU Ilmenau, GERMANY

Outline • Introduction: Test as Teaching Objective • Complexity vs. quality • Living pictures for learning logic level test • Low-cost tools for training digital test issues • Laboratory works and research training • Conclusions

Test Issues and Engineering Education • The importance of test (fault diagnosis) as a teaching objective is underestimated in traditional engineering education • Test is taught usually as a subtopic in a design course • It is taught as an independent discipline only when it is a hobby horse of the professor Why? • Because Test is interpreted as a nonproductive issue (vs. design) • The number of courses that should be taught at universities doubles in a decade(Tenhunen, EWME, Lausanne, April 2004)

Didactical Issues • Fault Diagnosis is not only an Electronics Systems related issue • It has an important didactive role for the engineering education in general: • It is a method to learn how to ask right questions • It develops the ability of analysingcause-effect relationships • It is looking for answers to the questions like what is thereason of what happened Logic world (digital systems) because of its inherent logical complexity could be the best objective for learning the concepts of diagnostic analysis for any technical systems in general

Introduction: Test Tools Test experiment Test result System (BIST) Fault simulation Fault diagnosis System model Fault dictionary Test Go/No go Located defect Test generation Test tools

Course Map for Teaching Test Theory Models Defect Level Boolean Differential Analysis Fault Modelling High Level Tools Fault Simulation Test Generation Fault Diagnosis DD BIST DFT Field: Test D&T Design High Level System Modelling Logic Level BDD

The Map of Research Topics “Defect-Oriented Hierarchical Test” Test Synthesis and Analysis Re-design Diagnosis Design for testability Self-Test Model Faults Defects Structure, functions Specification Design System

Research Motivation in the Field of Test The main question: How toimprove test quality at increasing complexities of today's systems? Solutions: • The complexity problems are handled by moving the abstraction levels from logicto higher functional or behavioral levels • To handle test quality in deep-submicron technologies, new fault models and defect-oriented methods should be used Confusing situation (deadlock): • High-level modelling reduces the accuracy (and quality of test) • Defect orientation increases the complexity

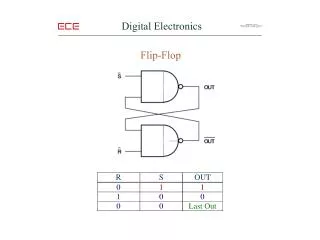

Defects and Complexity Stuck-at-1 Broken (change of the function) Bridging Stuck-open NewState Stuck-on (change of the function) Short (change of the function) Stuck-off (change of the function) Stuck-at-0 SAF-model is not able to cover all the transistor level defects How to model transistor defects ?

Hierarchical Approach to Test Problems Physical level Mapping of defects {Wd} dy Fault model: x1 x4 System level x2 Defect dy x3 x5 Component level Wd y* Error Logic level Hierarchical diagnostics

Teaching Tools • A set of tools will be presented for exercising Digital Test related problems like • test generation • fault simulation • fault diagnosis • built-in self-test • The tools and practical training are divided into three classes: • applets for preliminary learning of test topics on logic level • the tools for carrying out test related hands-on experiments (and research) for more complex circuits designed by students themselves

Methodology of Using Tools • A set of circuits as diagnostic objectives for the applets are predesigned and can be selected by the student • The applets can be used • by the teacher during the lecture, • by students for self-learning purposes, independent on the time and place, and again • by the teacher to give the tasks to students during exams • The third group of tools for hands-on experiments support reseach related laboratory work.

Living pictures • Test vector insertion panel • View panel for design schematics • View panel for displaying information (data tables, waveforms)

Fault Simulation Activated paths for selected test pattern Selected test pattern Fault table

Design panel: Small boxes on lines display internal signals The boxes are clickable during manual test vector generation and fault diagnosis In the test generation mode, the needed signal values for fault activation or fault propagation can be inserted at connections Test Pattern Generation

Procedure: Define the defect (bridging fault) Define the line affected by defect Sensitize the defect Propagate the fault Justify the values assigned to the lines Defect-Oriented Test Generation

Defect Investigation Environment DEFSIM Cooperation: Estonia, Germany, Poland DEFSIM SERVER USB DEFSIM INTERNET USER USER USER

Laboratory training by tools • After theoretical investigation of the test topics described in the previous section, a laboratory work follows with more complex designs, where • available design software (schematic editor as minimum), and • Turbo-Tester diagnostic software are used • Traditional VLSI test generation and fault simulation software on workstations are both costly and unable to handle large numbers of students simultaneously in educational courses • Low-cost systems for solving a large class of tasks from the dependability area - test synthesis and analysis, fault diagnosis, testability analysis, built-in self-test are missing

Laboratory training by tools Diagnostic software Turbo-Tester Fault models: Stuck-at-faults Stuck-opens Delay faults Methods: Single fault Parallel Deductive Methods: Deterministic Random Genetic Levels: Gate Macro Test Generation Fault Simulation Fault Location Design Test BIST Simulation Methods: BILBO CSTP Store/Generate Fault Table Fault Diagnosis Test Optimization

Laboratory training by tools • An advanced training environment TURBO TESTER has been developed at Tallinn Technical University • It is installed on PCs for teaching undergraduate and graduate courses in design for testability and test of digital electronics • TT is an easy-to-learn, easy-to-set-up and low-cost CAD system • It has interfacesto commercially available design tools like: Cadence, Synopsys, Mentor Graphics, Viewlogic, Compass, OrCAD, Dixi-CAD

Research-Oriented Lab Work • Built-in self-test (BIST) • BIST is the capability of a circuit to test itself • Students concentrate themselves in a off-line BIST consisting of a test pattern generator, unit under test and a response analyzer • There are several disadvantages of such a structure: • pseudorandom test sequences are usually very long • they do not guarantee always a sufficient fault coverage because of the existence of “hard-to-test” faults Test Pattern Generator Response Analyser Unit Under Test

Combining on-line generated pseudo-random patterns with pre-generated and stored test patterns Problems : To find the best characteristics for test generator (PRPG) To find the best level of mixing pseudo-random test and stored test as the tradeoff between memory cost and testing time Laboratory works Built-in self-test: SoC ROM . . . . . . Core Test Generator . . . . CORE UNDER TEST Controller Response Analyzer

Graphical solution for finding the optimum of mixing pseudorandom and stored test approaches as the tradeoff between the memory cost and testing time Cost of the BIST: CTOTAL = CTIME + CHW = TG + MS where CTIME is the cost related to time CHW is hardware cost related to BIST architecture, TG is the length of the test generated by hardware, MS is is the number of patterns to be stored Research training: Example

Conclusions • A conception is presented for improving the skills of students to be educated for digital test related topics • It is a combination of learning by • internet based simple “living pictures”, and • hands-on training with a set ofcommercial design tools, and low-cost university tools • The tools are accessible • Applets: http://www.pld.ttu.ee/testing/ • Low-cost test tools: http://www.pld.ttu.ee/tt/