The NA60 Experiment Readout Architecture

190 likes | 299 Vues

This paper presents the readout architecture of the NA60 Experiment, focusing on a new data acquisition system based on the PCI bus. It outlines the apparatus, data acquisition (DAQ) structure, and the electronics used for effective heavy ion and dimuon production detection at CERN's SPS. Key components include the muon spectrometer, trigger hodoscopes, and readout systems. The discussion covers the operational challenges faced and the validation process of the readout architecture, culminating in its successful implementation for data collection in August 2003.

The NA60 Experiment Readout Architecture

E N D

Presentation Transcript

The NA60 Experiment Readout Architecture M.Floris, D.Marras, G.Usai, A.David, P.Rosinsky, H.Ohnishi for the NA60 Collaboration 13th IEEE- NPSS Real Time Conference 2003, Hotel Omni Mont Royal, Montreal, Canada, May 18 – 23 2003

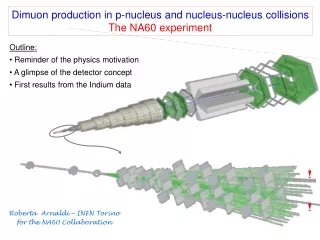

The NA60 Experiment LEP/LHC NA60 SPS • Fixed target experiment at CERN SPS • Heavy Ion / Dimuon experiment • Open charm and prompt dimuon production • Talk Outline: • Apparatus • DAQ Architecture • Readout Electronics • Conclusions 13th IEEE-NPSS Real Time Conference 2003

Detector Concept and Layout MUON SPECTROMETER ~1m Fe wall Tracking MWPCs Muon filter TARGET AREA Toroidal Magnet ZDC and Quartz Blade Trigger hodoscopes Dipole field2.5 T TARGET BOX MUON FILTER BEAM BEAMTRACKER IC TELESCOPE • 4 Detectors: • Muon Spectrometer (MWPCs, Trigger hodoscopes) • ZDC • Beam Tracker • Vertex Detector 13th IEEE-NPSS Real Time Conference 2003

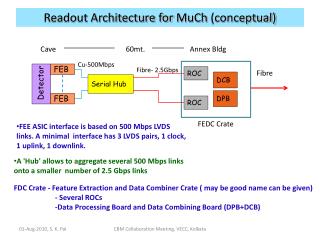

DAQ Overview burst burst interburst events - trigger Detector Detector Detector LDC DATE ALICE System is organized in indipendent partitions GDC Castor/ CDR 13th IEEE-NPSS Real Time Conference 2003

PCI System • Many partitions • A General-purpose PCI card • Many detector-specific mezzanines 13th IEEE-NPSS Real Time Conference 2003

Readout Chain Overview LDC DET.4 DET.3 DET.1 MEZZANINE 1 PCI Card PCI Card PCI Card PCI Card DET.2 MEZZANINE 2 INTERBURST PCI BUS MEZZANINE 3 LDC MEZZANINE 4 BURST Acquisition software (DATE) 13th IEEE-NPSS Real Time Conference 2003

Hardware/Software Handshake #3 #2 #1 #0 11 10 11 10 11 10 BURST At the end of the burst HW sets bit 2 bits 0-1: SPS status bit 2: R/O status bit3: timeout 00: idle 10: burst 11: interburst timeout SW starts as soon as bit 2 is set and resets it at the end If a new burst arrives while SW is still reading bit 3 is set Acquisition Software 13th IEEE-NPSS Real Time Conference 2003

PCI Card Architecture PCI interface CTRL RAM PCI INTERBURST mez. application Registers det. Control logic BURST PCI Card Light blue: blocks inside FPGA • FPGA • Large memory buffer • Mezzanine Cards • Registers 13th IEEE-NPSS Real Time Conference 2003

First Implementation – PCI-FLIC • Developed by EP/ED-DTb CERN Division • PCI core embedded in ORCA FPGA • Successfully used in test beams in 2001/2002 • Readout architecture validated • Has some limitations • Slow FPGA • Maintenance problems • A new card has been developed... 13th IEEE-NPSS Real Time Conference 2003

Final Implementation – PCI-CFD Will be used in next NA60 run • New and faster ALTERA FPGA • External PCI bridge (PLX 9030) • X4 bandwidth 64 MBytes RAM FPGA (APEX/ 20K100) PMC connectors for mezzanine cards PLX9030 PCI bridge 13th IEEE-NPSS Real Time Conference 2003

CFD – FPGA Application 31 0 errors # data words (8bit) Trailer marker word readout time data N data N - 1 data N - 2 Data data 5 data 4 data 3 data 2 data 1 time of arrival # burst # event Header # total words (8bit) # total words (8bit) Readout Event Formatting BURST RAM Writing INTER BURST PCI Interface 13th IEEE-NPSS Real Time Conference 2003

Mezzanine 1 – VME-Like & CAMAC Protocols • Very simple mezzanine • Level conversion ECL/NIM => TTL • Protocol itself implemented in PCI Card FPGA BUSY BURST WARNING TRIGGER PCI Card Protocol control signals & data 13th IEEE-NPSS Real Time Conference 2003

Mezzanine 1 – Protocols trigger start_read encode dflag data end_of_read • 2 different protocols implemented on this mezzanine: • RMH Protocol (Muon Spectrometer MWPCs & Hodoscopes) • Fera (CAMAC) protocol (Beam Tracker & ZDC) RMH Protocol 13th IEEE-NPSS Real Time Conference 2003

Mezzanine 2 - Pixel Detector GOL (Pix DATA) Pixel/PILOT (JTAG Conf.) Alice PILOT chip, radhard, Pixel chip configuration and readout, GOL interfacing GOL, radhard high speed serial link (GLink) alice ALICE1LHCb Pixel chip, radhard, 256x32 cells (425 mm x 50 mm) thanks… 13th IEEE-NPSS Real Time Conference 2003

Mezzanine 2 – Mezzanine Features • Complex mezzanine • Can be interfaced to 2 pixel planes • R/O implemented in local FPGA • Zero Suppression • Event formatting • Error detection • PCI accesses FIFOs • Detector configuration 13th IEEE-NPSS Real Time Conference 2003

Mezzanine 2 – Pixel Conf&Test Software • Mezzanine & pixel-chip configuration (JTAG) • Settings database • Detector & R/O Chip test • Threshold scan • Noisy and dead pixel • Used by DATE at run startup 13th IEEE-NPSS Real Time Conference 2003

Conclusions • A new readout system based on the PCI bus has been developed for a HEP experiment • High performances and flexibility, low costs • Roadmap: • Muon spectrometer electronics commissioned October 2001 • Beam Tracker and ZDC electronics used for the first time June 2002 • Pixel Telescope intermediate system working on beam June & October 2002 • Final system working in lab, will be used in data taking August 2003 13th IEEE-NPSS Real Time Conference 2003

Acknowledgements • The authors would like to thank the following people: • CERN EP/ED-DTb group and in particular Hans Muller for their contributions and suggestions in the early stages of the project • The Alice Pixel group and in particular F.Formenti, G.Stefanini, K.Wyllie, A.Kluge and M.Burns for their constant support to the NA60 pixel project 13th IEEE-NPSS Real Time Conference 2003

NA60 Collaboration CERN Bern Palaiseau Riken BNL Yerevan Stony Brook Torino Lisbon Cagliari Clermont Lyon R. Arnaldi, K. Banicz, K. Borer, J. Buytaert, J. Castor, B. Chaurand, W. Chen, B. Cheynis,C. Cicalò, A. Colla, P. Cortese, A. David, A. de Falco, N. de Marco, A. Devaux, A. Devismes,A. Drees, L. Ducroux, H. En’yo, A. Ferretti, M. Floris, P. Force, A. Grigorian, J.Y. Grossiord,N. Guettet, A. Guichard, H. Gulkanian, J. Heuser, M. Keil, L. Kluberg, Z. Li, C. Lourenço,J. Lozano, F. Manso, A. Masoni, A. Neves, H. Ohnishi, C. Oppedisano, G. Puddu, E. Radermacher, P. Rosinský, E. Scomparin, J. Seixas, S. Serci, R. Shahoyan, E. Siddi, P. Sonderegger, G. Usai, H. Vardanyan and H. Wöhri 50 people, 12 institutes, 7 countries 13th IEEE-NPSS Real Time Conference 2003