Enhancements in G-Link Emulation and Memory Management for Virtex-6 in CMM Code Development

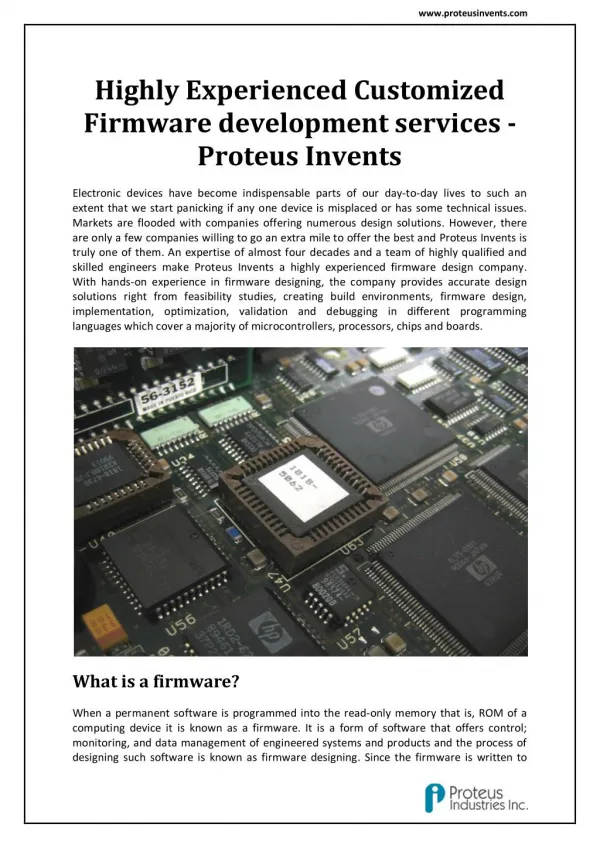

This documentation details recent advancements in the porting of CMM code to the Virtex-6 platform, focusing on G-Link emulation and GTX serializer integration. Two versions, VC and VS, are introduced. Key updates include adaptations of the clock tree to utilize MMCM, an upgrade to block RAM within the readout FIFO, and comprehensive testing conducted via Xilinx ISIM. Simulation results show zero errors in the DAQ and ROI data handling, ensuring that latency remains consistent. The design's effective simulation validates its reliability for further development.

Enhancements in G-Link Emulation and Memory Management for Virtex-6 in CMM Code Development

E N D

Presentation Transcript

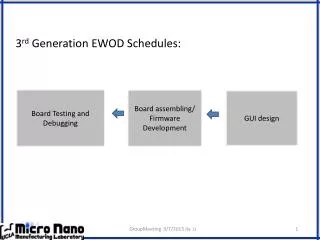

CMX firmware development Pawel Plucinski Stockholm University • CMX firmware status • G-Link and GTX serializer • Clock manager • Memory • Conclusions

CMM code – the port to the V6 Recent changes and tests CMM code – the port to the V6. This includes: • Two versions: VC and VS. • G-link emulation + serializer GTX (including ISIM and scope tests of the optical output; target ML605 - xc6vlx240t). • Adapting the clock tree to the Virtex-6 MMCM. • Updating the block RAM implementation in the readout fifo/memory. • Successfully simulated (ISIM).

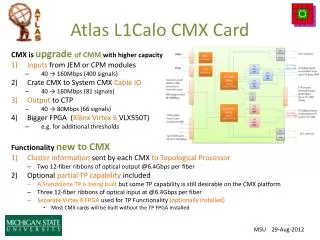

G-link emulation in Virtex 6 General idea DAQ or ROI data word Encodedword G-link encoder 24b 8b multiplexer GTX TX 20b 24b 960 Mbs 8b DAV(data available) 40 MHz 40 MHz 120 MHz 120 MHz

G-link emulation in Virtex 6 The readout scheme DAQ_IN G-link encoder Mux GTX TX daq_enc daq_byte daq_out 20b DAQ_DAV 2b 24b 8b DAQ_RST clk40 clk40 clk120 clk120 ROI_IN G-link encoder GTX TX roi_byte roi_out roi_enc 20b ROI_DAV 2b 24b 8b ROI_RST clk40 clk40 clk120 clk120 clk40 clk120

G-link emulation in Virtex 6 Behavioral simulation results Reset non zeros data DAV asserted Empty frames Sending zeros This test was done with Xilinx ISIM...

G-link emulation in Virtex 6 “An eye diagram” Scope tests of the optical output (target ML605): Good result: Rise and Fall time below 240 psec!

CMM code – the port to the V6 Adapting the clock tree (MMCM)

CMM code – the port to the V6 Updating the block RAM Memory type: True Dual Port RAM Write/Read Width:16b Write/Read Depth:256

CMM code – the port to the V6 Simulation results: cmm_jepcrt_vc No errors DAQ data Testbench with random input data (no errors).

CMM code – the port to the V6 Simulation results: cmm_jepcrt_vs Readout enable DAQ and ROI data No errors Testbench with random input data (no errors).

Conclusion • 'Jet-CMM emulation' design for Virtex-6 on the CMX: two versions 'vc' and 'vs', available on SVN. • G-link protocol + GTX serializer is added • The Clock tree is updated. The clock manager (MMCM) is being used. • 'A new block RAM' in the readout fifo/memory implemented. • Design was successfuly simulated with ISIM (testbunch, random input data, no errors). • Latency is unchanged.