Performance Tracking and Link Setup for SCT Operation and Quality Assurance

This document details the operational performance tracking and link setup procedures for the SCT system, emphasizing the importance of proper configuration during operation. Key challenges such as operational difficulties, fatalities, and the impact of VCSEL parameters on performance are analyzed. This includes procedures for setting TX and RX links, optimal DAC settings, and the importance of a robust QA process. Contributions from experts in the field are acknowledged, and various tests are explored to ensure reliable data transmission and minimize bit errors.

Performance Tracking and Link Setup for SCT Operation and Quality Assurance

E N D

Presentation Transcript

SCT Links Operation • Performance from QA and operation • Setting up links during operation for barrel and EC. • TX • RX • Operational problems • Fatalities • Difficulties • How can we track performance? • Acknowledgements • thanks to Peter Phillips, Bilge Demirkoz, Caroline Magrath and Nigel Hessey for discussions of SCT procedures Pixel Opto November '06

Performance from QA • On-detector VCSEL power • Two VCSELs in one opto-package have single VCSEL current setting Spread of power between two VCSELs important. Pixel Opto November '06

PIN Arrays & DRX-12 Count bit errors in 32k bit stream Blue region is error free. • Slow tail to signal limits dynamic range • Saturation of DRX-12 at very high input current ~ 800 mA Pixel Opto November '06

RX links dynamic range (1) • RX link designed to work at power > 40 mW • Only tested on one channel but could operate with negligible BER at 35 mW (no error in 1 hour) Bit Error Rate Scans Different Optical power BER RX DAC

RX links dynamic range (2) • Look at range of RXmax/RXmin • Can’t set RXmax > 255 Need RXmin < 100 reasonable operating window RXmax ~ 500 Power ~ 1000 mW • Would be better to have a larger range for DRX-12 threshold but can only easily increase this by 20%. Does this help? • However system should work over dynamic range > ~ 10. • Is this true in practice? Pixel Opto November '06

Off-Detector VCSELs • High mean power but large spread. • Change 10 mA 15 mA increases power by ~50% Pixel Opto November '06

Setting Up Links • TX links • Initially set TX DAC = 165 nominal VCSEL current of 10 mA. Newer TXs have higher fibre coupled power new default TX DAX = 140 • Check IPIN. Adjust if <100 (200) or > 700 (600) mA for barrel (EC). • Usually ok after this but if there are problems perform TX DAC scan (see later). Pixel Opto November '06

RX Links • DC coupled links are more difficult to set-up. • Old procedure for barrel • Perform RX threshold scan. • Send configuration data and repeat for 10 triggers (8000 bits). Change RX DAC value and repeat coarse scan of BER vs RX DAC. Optimal setting RX_DAC=0.3*RXmin+0.7*RXmax figure. Works but is slow. • Set timing to global value (barrel) or perform RXdelay scan (Endcaps). • New method: superfast scan (7s) • 2d scan of delay and Rxthreshold in clock/2 mode (ABCD returns 20 MHz clock). Works for most modules but use slower Rxthreshold based on configuration data for problematic channels. Pixel Opto November '06

RX threshold Scan • Good links wide operating window. Not typical! Most VCSEL too bright so don’t see top edge of scan. RX_Threshold Errors at low RX DAC are not due to noise but are due to the slow tail in the p-i-n signals (off-detector array). RXmin scales with power Pixel Opto November '06 Time Bin

MSR Adjustment (1) • Need accurate 50:50 MSR for 20 MHz clock low jitter BC clock recovered by DORIC don’t try to design perfect clock but allow for adjustments with MSR register. • Adjustment will be required on all channels to optimise timing but if it is very wrong can cause problems even in calibration runs. i/p clock with non 50:50 MSR o/p clock has large jitter Pixel Opto November '06

MSR Adjustment (2) • MSR adjustment can work produce low jitter BC clock. Obtain jitter (full width) < 0.5 ns for optimal MSR but jitter could be very big if MSR wrong • Warning: we found a few VCSEL arrays that had very low MSR and could not be tuned to give 50:50 MSR Register

MSR Adjustment (3) • How to set MSR values in full system? • Idea is to tune system so that duty cycle of clock/2 is independent of BPM phase. • MSR scan • (1) Set clock/2 mode • (2) SetMSR value • (3) Measure width of on period with scan of RXdelay. • (4) send odd number of bits (SR) of TTC data to flip phase of BPM signal and repeat (3) • (5) Change MSR register 3 • (6) Plot duty cycle for the two phases as a function of MSR register figure • Plan to develop faster 2D scan in future Pixel Opto November '06

MSR Adjustment (4) • Scan does work but is very time consuming. Only use it now if we have problems with calibration runs

Operational Problems • Fatalities • ESD deaths. ~ 0.4 % of on-detector VCSELs died after burn-in (72 hours @ 10 mA and 50C and full QA (~ 30 minutes operation) rely on redundancy. Maybe lower level damage on more VCSELs will compromise the lifetimes? • Slow turn on VCSELs (figure). QA used DC or PSBR data. Real operation involves long gaps between bursts of data. ~ 0.25% of on-detector VCSELs are not usable. Pixel Opto November '06

Slow Turn on VCSEL • Link 1 has no good value for RX DAC use redundancy • Link 0 illustrates intermediate case: can find good RX DAC but lose dynamic range. Pixel Opto November '06

Operational Problems • Difficulties • RX links: Intermediate cases of slow turn on VCSELs can be used but much more care required to set Rxthreshold slow scan. • TX links: some require larger IPIN than normal, may be linked to slow turn on off-detector VCSELs? Pixel Opto November '06

Problem Solving Recipes • Runs do crash. Often after many minutes in noise occupancy scans because long events suffer more from slow turn on VCSEL problems. • Fixes • Hard reset ( module CLK/2) and repeat • If RXmin>100 reduce VCSEL current • If RXmin<100 increase VCSEL current • Redo RX threshold scan and RX delay scan. • Look at error codes: if they are L1 or BC ID errors error at start of run probably slow turn on VCSEL. • perform TXscan: scans TX DAC value and sends and returns configuration data (cf RX threshold scan). Increase or decrease IPIN if necessary. • (ABCD errors increase VDD to 4.2V) • Have succeeded in simultaneous operation of large number of modules: 672 Barrel 6 in Oxford and 462 barrel modules in SR1 Cosmic run but required a lot of tweaking of parameters. Pixel Opto November '06

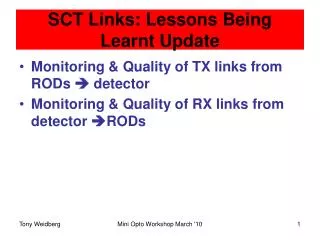

Tracking Performance • TX links • Measure IPIN and check if we see expected decrease in responsivity with radiation damage • RX links. • Can track performance roughly with RXmin fig. • Better if we could measure I_PIN in array for each channel Pixel Opto November '06

Tracking I(p-i-n) Difference I(p-i-n) in a run cf reference run. Mean change in I(p-i-n) versus run number 10% spread due to off-detector VCSEL variation but means show stability over ~ 2 months Pixel Opto November '06

RX min correlation with Power Weak correlation Better way: use current measurement in off-detector p-i-n array 12 bits with LSB = 6 mA ~ O(2%) precision.

Outlook • Should take time to debug anomalous channels. • Look at signals with optical probe. • Easier to debug in SR1 than in pit • Can we make DAQ more robust so that single bit errors don’t cause system to crash in calibration runs? Pixel Opto November '06