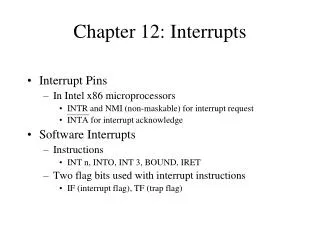

Chapter 12: Interrupts

Chapter 12: Interrupts. Interrupt Pins In Intel x86 microprocessors INTR and NMI (non-maskable) for interrupt request INTA for interrupt acknowledge Software Interrupts Instructions INT n, INTO, INT 3, BOUND, IRET Two flag bits used with interrupt instructions

Chapter 12: Interrupts

E N D

Presentation Transcript

Chapter 12: Interrupts • Interrupt Pins • In Intel x86 microprocessors • INTR and NMI (non-maskable) for interrupt request • INTA for interrupt acknowledge • Software Interrupts • Instructions • INT n, INTO, INT 3, BOUND, IRET • Two flag bits used with interrupt instructions • IF (interrupt flag), TF (trap flag)

Interrupt Vectors • Interrupt vector table located at addresses 000000H to 0003FFH Interrupt vector contains segment and offset address of interrupt service routine (ISR)

PUSH and POP PUSH BX : SP <- SP-2 POP CX : SP <- SP+2

Cyclic Nature in PUSH/POP • PUSH CX ; cyclic address calculation

Interrupt Activation • From external source • Set INTR pin or a positive edge (0-to-1) on the NMI pin • Checked once (at the beginning or at the end) during the CPU’s instruction execution cycle • Cannot be checked during the “middle” of the execution of another instruction – wait until before fetch of next instruction • From internal source • Execution of INT, INTO, INT 3, or BOUND instruction • E.g., INT 3 calls the interrupt service routine at 00CH (=3*4) in the interrupt vector table

Operation of Real Mode Interrupt • Disable interrupts • Clear IF and TF bits in the flag register • Disables the INTR pin and trap (single-step) • Save the current state • Push flag register onto the stack • Push CS onto the stack • Push IP onto the stack • If the processor has more state registers, e.g., register file, they are also stored in the stack • Far call to interrupt service routine (ISR) • Fetch interrupt vector contents and store into IP and CS • Next instruction executes from the ISR • Return from ISR • IRET instruction restores the stored state in the stack

Normal Far CALL vs. ISR Execution Flag is stored Destination address comes from interrupt vector table

Flag Register C(carry) : holds the carry after addition or the borrow after subtraction P(parity) : 0 for odd, 1 for even parity A(auxiliary carry) : holds the carry or borrow between bit 3 and 4 Z(zero) : 1(result is 0), 0(result is not zero) S(sign) : 0(positive), 1(negative) T(trap) : enables trapping after each instruction for on-chip debugging I(interrupt) : enables(1) or disables(0) interrupt request from INTR pin D(direction) : increment(0) or decrement(1) of DI/SI for string instructions O(overflow) : out of range(1) of signed numbers operation

Examples of Flag Bits • Overflow V = C4 XOR C5 Scheme of Parallel Adder

Interrupt Flag Bits • FLAG register includes I (bit 9) and T (bit 8) flag bits • When I bit is set, interrupts through the INTR pin are accepted • Set using “STI” assembly instruction • Reset using “CLI” assembly instruction • When TF bit is set, it causes a trap interrupt (type number 1) to occur after each instruction executes • Single-stepping • Useful for debugging • Set or reset by setting/resetting that bit in the FLAG register directly

Identifying Interrupt Vector • The device which caused the interrupt gives the interrupt vector to the processor via data bus • Timing shown • INTR INTA vector number on D7-D0

Simple Generation of Interrupt Vector 16 D15-D0 D7-D0 8 uP tri-state buffer O7-O0 G INTA I7-I0 VCC

Interrupt Priority Control • Software Polling • Single interrupt vector (ISR) • Easy to change by program • Slow response • Daisy Chain • Connected in series • Simple hardware connection • Lowest-priority I/O may have to wait too long. • Simple logic gates • Equivalent to daisy chain method • Can be used for small system • Multiple Interrupt Lines • Fast response • Complicated hardware • Limited number of I/O

Polling CPU polls the status register of I/O by a program. CPU ADDR DATA INTR IR IR IR IR I/O Controler1 I/O Controler2 I/O Controler3 I/O Controler4

Daisy Chain CPU ADDR DATA INTR INTA IR IR IR IR INTA GRNT INTA GRNT INTA GRNT INTA GRNT I/O Controler1 I/O Controler2 I/O Controler3 I/O Controler4

Daisy Chain with Logic Gates CPU D7-D0 DATA 8 Two Interrupt vectors 00000001 : higher priority 00000000 : lower priority O7-O0 G INTA I7-I0 GND IR0 INTR IR1

Multiple Interrupt Lines CPU ADDR DATA IR1 IA1 IR2 IA2 IR3 IA3 IR4 IA4 IR IR IR IR INTA INTA INTA INTA I/O Controller1 I/O Controller2 I/O Controller3 I/O Controller4

I/O Interface with I/O Controller ADDR DATA CPU Control I/O Controller 1 I/O Controller 2 I/O Controller 3 Status Ctrl Data Status Ctrl Data Status Ctrl Data I/O 1 I/O 2 I/O 3 I/O controller - Communicates with general CPU(fast) and dedicated I/O device(slow). - Adjusts timing by handshaking. - Performs as a temporary data buffer.