FPGA Solutions ...

E N D

Presentation Transcript

FPGA Solutions ... FPGA and LabVIEW Pattern Generator Multi-Channel-Scaler Dietrich Beck

Field Programmable Gate Array perform logic operations in hardware behavior defined by "Programmable Interconnects" no CPU (that is executing commands) no "software" no operating system real "hardware" real time: hardware logic real parallelism re-configurable hardware don't buy specific hardware for a specific task buy general purpose FPGA hardware to perform specific tasks need less spares FPGA Dietrich Beck

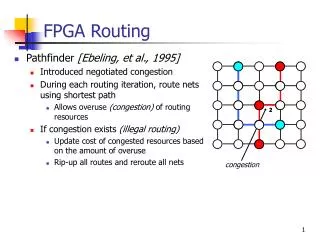

VHDL (VeryHighSpeedIntegratedCircuit Hardware Description Language) as standard approach to FPGA programming specific tool chain of FPGA manufacturer converts VHDL code to configuration of the logic blocks ("bit-file") on the FPGA FPGA @ National Instruments someone programs LabVIEW using FPGA specific function palettes FPGA module generates VHDL code from LabVIEW code VHDL code is given to tool chain of manufacture (here: Virtex) bit-file is written to hardware Programming an FPGA Dietrich Beck

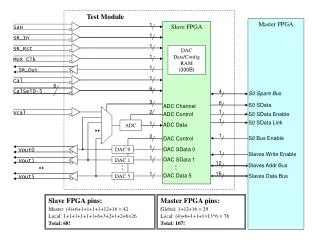

task: produce bit patterns at given times example 8 digital outputs: one byte bit pattern (10000000) each bit is used as trigger signal for external hardware switch between patterns at specified times 10000000 @ t = 0 s 10000001 @ t = 1.2s 11000101 @ t = 235246.875s .... real parallelism: outputs of all bits synchronized hard real time: timing determined by FPGA clock Pulsed Pattern Generator (PPG) Dietrich Beck

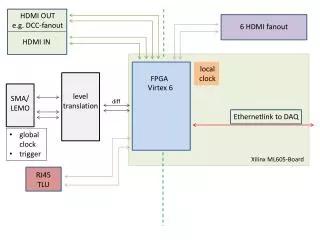

two solutions based on NI PCI-7811R (1400,- €) 160 digital I/Os, Virtex II, one million gates, 40 MHz clock synchronization to external reference clock only with PXI version same starting point for two solutions by Stephen Koszudowski, GSI customized to "standard trap software" no general interface by Falk Ziegler, Uni-Greifswald general interface can not be used by "standard trap software" in a straight forward way difficulty due to specific pattern definition format in "standard trap software" PPG Status 2008 Dietrich Beck

use solution from Falk Ziegler as starting point only little effort required for usage as general solution implemented as device class within the CS-framework implement interface to "standard trap software" by inheriting from the general class maintained by KS/EE PPG Proposition for Unified Solution Dietrich Beck

PPG Proposed Changes Dietrich Beck

change pin assignment (Uni-Greifswald) change treatment of trigger (Uni-Greifswald) change of "idle state" (Uni-Greifswald) clean-up handling of PPG in sequencer ( of "standard trap solution") PPG Consequences Dietrich Beck

task: time resolved counting of ions (photons, ...) motivation: existing solution using an SR430 from SRS is quite expensive. We don't need the full functionality of the SR430. three TTL I/O start trigger (input, positive edge, logic high) signal (input, positive edge, logic high) isActive (output, logic high while counting) FPGA over-clocked to 80 MHz minimum time for active high is 12.5 ns maximum count rate 40 MHz requires "NIM-electronics-type" discriminator and delay-gate. simple FPGA program and instrument driver class of driver inheriting from base-class so far, only used in test set-up Multi-Channel-Scaler (MCS) Dietrich Beck

... ... vacuum safety? Other Ideas Dietrich Beck