Finite State Machines: VHDL Example of Detecting Sequence 1101 with Mealy and Moore Machines

280 likes | 401 Vues

This document discusses Finite State Machines (FSM) using VHDL to illustrate how to detect the input sequence "1101" with both Mealy and Moore machines. It details the design and implementation of the state machines, including the state registers, present and next states, and processes triggered by clock signals. The example highlights both combinational and sequential networks, showcasing the processes involved in detecting sequences and outputs based on different input conditions. This is a practical guide for understanding FSMs through VHDL.

Finite State Machines: VHDL Example of Detecting Sequence 1101 with Mealy and Moore Machines

E N D

Presentation Transcript

Finite State Machines Discussion D8.1 Example 36

init Combinational Network s(t+1) s(t) State Register next state present state x(t) present input present output clk z(t) Canonical Sequential Network

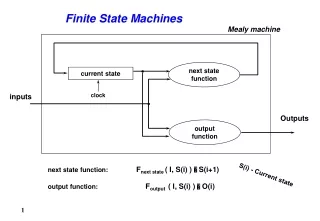

init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input clk Mealy Machine

init C2 C1 z(t) s(t+1) State Register next state s(t) present state x(t) present input clk Moore Machine

VHDLCanonical Sequential Network init Combinational Network s(t+1) s(t) State Register next state present state x(t) present input process(clk, init) present output clk z(t) process(present_state, x)

VHDLMealy Machine process(present_state, x) init C1 C2 s(t+1) State Register next state s(t) z(t) present state x(t) present input process(present_state, x) clk process(clk, init)

VHDLMoore Machine init C2 C1 z(t) s(t+1) State Register next state s(t) present state x(t) present input process(present_state, x) process(present_state) clk process(clk, init)

ExampleDetect input sequence 1101 fsm din clk dout clr din dout 1 0 1 1 0 1 1 0 1 0 0 1 1 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 1 0

0 1 1 0 0 1 CLR 0 1 0 1 Use State DiagramDetect input sequence 1101 S1 0 S0 0 S11 0 S1101 1 S110 0

fsm.vhd fsm din clk dout clr

clr dout din fsm.vhd

clr dout din fsm.vhd

S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1 fsm.vhd

fsm.vhd S1 0 0 1 1 S0 0 0 S11 0 0 CLR 1 0 1 0 S1101 1 S110 0 1

clr dout din fsm.vhd

fsmx.vhd ld(0) ld(1) din fsm dout clr ld(7) btn(3) clk btn(1) bn clk_pulse btn(0) fsmx cclk mclk clkdiv

fsmx.vhd entity fsmx is port( mclk : in STD_LOGIC; sw : in STD_LOGIC_VECTOR(7 downto 0); btn : in STD_LOGIC_VECTOR(3 downto 0); ld : out STD_LOGIC_VECTOR(7 downto 0); a_to_g : out STD_LOGIC_VECTOR(6 downto 0); dp : out STD_LOGIC; an : out STD_LOGIC_VECTOR(3 downto 0) ); end fsmx;

fsmx.vhd component clock_pulse port( inp : in std_logic; cclk : in std_logic; clr : in std_logic; outp : out std_logic); end component; signal clr, clk, cclk, bn: std_logic; signal clkdiv: std_logic_vector(23 downto 0);

fsmx.vhd bn <= btn(1) or btn(0); clr <= btn(3); U0: clk_pulse port map (inp => bn, cclk => cclk, clr =>clr, clk => clk); U1: fsm port map (clr =>clr, clk => clk, din => btn(1), dout => ld(7)); ld(0) <= BTN(0); ld(1) <= BTN(1);

-- Example 36b: Detect 1101 with Mealy machine library IEEE; use IEEE.STD_LOGIC_1164.all; entity seqdetb is port (clk: in STD_LOGIC; clr: in STD_LOGIC; din: in STD_LOGIC; dout: out STD_LOGIC); end seqdetb; architecture seqdetb of seqdetb is type state_type is (s0, s1, s2, s3); signal present_state, next_state: state_type; begin

sreg: process(clk, clr) begin if clr = '1' then present_state <= s0; elsif clk'event and clk = '1' then present_state <= next_state; end if; end process;

C1: process(present_state, din) begin case present_state is when s0 => if din = '1' then next_state <= s1; else next_state <= s0; end if; when s1 => if din = '1' then next_state <= s2; else next_state <= s0; end if; when s2 => if din = '0' then next_state <= s3; else next_state <= s2; end if; when s3 => if din = '1' then next_state <= s1; else next_state <= s0; end if; when others => null; end case; end process;

Seq2: process(clk, clr) begin if clr = '1' then dout <= '0'; elsif clk'event and clk = '1' then if present_state = s3 and din = '1' then dout <= '1'; else dout <= '0'; end if; end if; end process; end seqdetb; Note that dout is a registered output dout