COMP541 Combinational Logic - 3

COMP541 Combinational Logic - 3. Montek Singh Jan 21, 2010. Topics. Other gates, XOR X’s – don’t cares Using encoder as example Z’s – floating values Multiplexers and Decoders Quick look at timing and glitches. Other Types of Gates. In practical terms, doesn’t matter for our FPGA

COMP541 Combinational Logic - 3

E N D

Presentation Transcript

COMP541Combinational Logic - 3 Montek Singh Jan 21, 2010

Topics • Other gates, XOR • X’s – don’t cares • Using encoder as example • Z’s – floating values • Multiplexers and Decoders • Quick look at timing and glitches

Other Types of Gates • In practical terms, doesn’t matter for our FPGA • But does for other technologies

Exclusive OR • Exclusive OR • What lay people mean by “or” • Symbol is • Plus in a circle

Parity Function • Recall how parity works • Ask class • Write truth table for two input even parity • What needs to be generated for parity bit? • What function of two inputs gives you this?

XOR Gives Odd Function • As many inputs as necessary • How do you get odd parity? • Design even parity generator for 3-bit signal • Perhaps make truth table and K-Map • Draw with XOR, then sum-of-products w/ NAND gates • How do you design a detector? • How about a 7-bit ASCII character?

CMOS Transmission Gates • Act like electronic switches

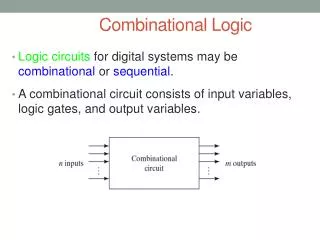

Introduction to Circuits • A logic circuit is composed of: • Inputs • Outputs • Functional specification • Timing specification

Circuits • Nodes • Inputs: A, B, C • Outputs: Y, Z • Internal: n1 • Circuit elements • E1, E2, E3 • Each a circuit

Types of Logic Circuits • Combinational Logic • Memoryless • Outputs determined by current values of inputs • Sequential Logic • Has memory • Outputs determined by previous and current values of inputs

Rules of Combinational Composition Composition rules: • Every circuit element is itself combinational • Every node of the circuit is either designated as an input to the circuit or connects to exactly one output terminal of a circuit element • no output shorts • The circuit contains no cyclic paths • every path through the circuit visits each circuit node at most once (latches are made via a cyclic path) • Example:

Aside: Circuit Schematics with Style Drawing style/conventions: (where possible) • Inputs are on the left (or top) side of a schematic • Outputs are on the right (or bottom) side of a schematic • Gates should flow from left to right • Straight wires are better to use than jagged wires

Circuit Schematic Rules (cont.) Wire connections • A dot where wires cross indicates a connection • Wires crossing without a dot make no connection • Wires always connect at a T junction

Multiple Output Circuits Output asserted corresponding to most significant TRUE input

Meanings of X • Don’t care • Contention (illegal input value) • Uninitialized value • In a simulator

Floating: Z • Floating, high impedance, open, high Z • Floating output might be 0, 1, or somewhere in between • A voltmeter won’t indicate whether a node is floating • Allows connecting outputs Tristate Buffer

Combinational Building Blocks • Multiplexers • Decoders • Encoders

Multiplexer (Mux) • Selects between one of N inputs to connect to the output. • log2N-bit select input – control input • Example: 2:1 Mux

Multiplexer Implementations • Logic gates • Sum-of-products form • Tristates • For an N-input mux, use N tristates • Turn on exactly one to select the appropriate input

Multiplexer with Hi-Z Normal operation is blue area Smoke

Logic using Multiplexers • Using the mux as a lookup table

Verilog for Multiplexer • Just a conditional statement. For example, module mux2(input [3:0] d0, d1, input s, output [3:0] y); assign y = s ? d1 : d0; endmodule

Decoders • N inputs, 2N outputs • “One-hot” outputs • only one output HIGH at any time

Aside: Enable • Enable is a common input to logic functions • See it in memories and today’s logic blocks

Decoders • How about a… • 1-to-2 decoder? • 3-to-8 decoder? • (N+1)-to-2(N+1) decoder?

3-to-8 Decoder: Truth Table • Notice they are minterms

Uses for Decoders • Binary number might serve to select some operation • CPU op codes are encoded • Decoder lines might select add, or subtract, or multiply, etc. • Memory address lines

Logic using Decoders • OR the ON-set minterms

Demultiplexer • Takes one input • Out to one of 2n possible outputs

Demux is a Decoder • With an enable

Encoder • Encoder is the opposite of decoder • 2n inputs (or fewer) • n outputs

Inputs are Minterms • Can OR them together appropriately • A0 = D1 + D3 + D5 + D7

What’s the Problem? • What if D3 and D6 both high? • Simple OR circuit will set A to 7

Priority Encoder • Chooses one with highest priority • Largest number, usually • Note “don’t cares” What if all inputs are zero?

Need Another Output • A “Valid” output

Code Converters • One code to another • Book puts seven-segment decoder in this category • Typically multiple outputs • Each output has function or truth table

Seven-Segment Decoder • LAST Friday’s lab: Verilog of hex to LEDs • Extended version of book example