VLSI Arithmetic Adders & Multipliers

1.23k likes | 1.48k Vues

VLSI Arithmetic Adders & Multipliers. Prof. Vojin G. Oklobdzija University of California http://www.ece.ucdavis.edu/acsel. Digital Computer Arithmetic belongs to Computer Architecture, however, it is also an aspect of logic design

VLSI Arithmetic Adders & Multipliers

E N D

Presentation Transcript

VLSI ArithmeticAdders & Multipliers Prof. Vojin G. Oklobdzija University of California http://www.ece.ucdavis.edu/acsel VLSI Arithmetic

Digital Computer Arithmetic belongs to Computer Architecture, however, it is also an aspect of logic design The objective of Computer Arithmetic is to develop appropriate algorithms that are utilizing available hardware in the most efficient way. Ultimately, speed, power and chip area are the most often used measures, making a strong link between the algorithms and technology of implementation. Introduction VLSI Arithmetic

Addition Multiplication Multiply-Add Division Evaluation of Functions Basic Operations VLSI Arithmetic

Addition of Binary Numbers Full Adder. The full adder is the fundamental building block of most arithmetic circuits: The sum and carry outputs are described as: ai bi Full Adder Cout Cin si VLSI Arithmetic

Inputs Outputs ci ai bi si ci+1 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Addition of Binary Numbers Propagate Generate Propagate Generate VLSI Arithmetic

Full-Adder Implementation Full Adder operations is defined by equations: Carry-Propagate: and Carry-Generate gi One-bit adder could be implemented as shown VLSI Arithmetic

High-Speed Addition One-bit adder could be implemented more efficiently because MUX is faster VLSI Arithmetic

The Ripple-Carry Adder VLSI Arithmetic

The Ripple-Carry Adder From Rabaey VLSI Arithmetic

Inversion Property From Rabaey VLSI Arithmetic

Minimize Critical Path by Reducing Inverting Stages From Rabaey VLSI Arithmetic

Manchester Carry-Chain Realization of the Carry Path • Simple and very popular scheme for implementation of carry signal path VLSI Arithmetic

Manchester Carry Chain • Implement P with pass-transistors • Implement G with pull-up, kill (delete) with pull-down • Use dynamic logic to reduce the complexity and speed up Kilburn, et al, IEE Proc, 1959. VLSI Arithmetic

Ripple Carry Adder Carry-Chain of an RCA implemented using multiplexer from the standard cell library: Critical Path Oklobdzija, ISCAS’88 VLSI Arithmetic

Pass-Transistor Realization in DPL VLSI Arithmetic

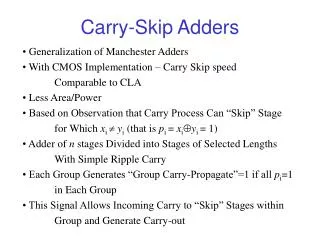

Carry-Skip Adder MacSorley, Proc IRE 1/61 Lehman, Burla, IRE Trans on Comp, 12/61 VLSI Arithmetic

Carry-Skip Adder Bypass From Rabaey VLSI Arithmetic

Carry-Skip Adder:N-bits, k-bits/group, r=N/k groups VLSI Arithmetic

Carry-Skip Adder k VLSI Arithmetic

Variable Block Adder(Oklobdzija, Barnes: IBM 1985) VLSI Arithmetic

Carry-chain of a 32-bit Variable Block Adder(Oklobdzija, Barnes: IBM 1985) VLSI Arithmetic

Carry-chain of a 32-bit Variable Block Adder(Oklobdzija, Barnes: IBM 1985) 6 5 5 4 4 3 3 D=9 2 2 1 1 Any-point-to-any-point delay = 9 D as compared to 12 D for CSKA VLSI Arithmetic

Carry-chain block size determination for a 32-bit Variable Block Adder(Oklobdzija, Barnes: IBM 1985) VLSI Arithmetic

Delay Calculation for Variable Block Adder(Oklobdzija, Barnes: IBM 1985) Delay model: VLSI Arithmetic

Variable Block Adder(Oklobdzija, Barnes: IBM 1985) Variable Group Length Oklobdzija, Barnes, Arith’85 VLSI Arithmetic

Carry-chain of a 32-bit Variable Block Adder(Oklobdzija, Barnes: IBM 1985) Variable Block Lengths • No closed form solution for delay • It is a dynamic programming problem VLSI Arithmetic

Delay Comparison: Variable Block Adder(Oklobdzija, Barnes: IBM 1985) VLSI Arithmetic

Delay Comparison: Variable Block Adder VBA CLA VBA- Multi-Level VLSI Arithmetic

Fan-Out Dependency VLSI Arithmetic

Fan-In Dependency VLSI Arithmetic

Delay Comparison: Variable Block Adder(Oklobdzija, Barnes: IBM 1985) VLSI Arithmetic

Carry-Lookahead Adder(Weinberger and Smith) Weinberger and J. L. Smith, “A Logic for High-Speed Addition”, National Bureau of Standards, Circ. 591, p.3-12, 1958. VLSI Arithmetic

Carry-Lookahead Adder(Weinberger and Smith) VLSI Arithmetic

Carry-Lookahead Adder One gate delay D to calculate p, g One D to calculate P and two for G Three gate delays To calculate C4(j+1) Compare that to 8 D in RCA ! VLSI Arithmetic

Carry-Lookahead Adder(Weinberger and Smith) Additional two gate delays C16 will take a total of 5D vs. 32D for RCA ! VLSI Arithmetic

32-bit Carry Lookahead Adder VLSI Arithmetic

Carry-Lookahead Adder(Weinberger and Smith: original derivation ) VLSI Arithmetic

Carry-Lookahead Adder(Weinberger and Smith: original derivation ) VLSI Arithmetic

Carry-Lookahead Adder (Weinberger and Smith)please notice the similarity with Parallel-Prefix Adders ! VLSI Arithmetic

Carry-Lookahead Adder (Weinberger and Smith)please notice the similarity with Parallel-Prefix Adders ! VLSI Arithmetic

Delay Optimized CLA B. Lee, V. G. Oklobdzija Journal of VLSI Signal Processing, Vol.3, No.4, October 1991 VLSI Arithmetic

Delay Optimized CLA: Lee-Oklobdzija ‘91 (a.) Fixed groups and levels (b.) variable-sized groups, fixed levels (c.) variable-sized groups and fixed levels (d.) variable-sized groups and levels VLSI Arithmetic

Two-Levels of Logic Implementation of the Carry Block VLSI Arithmetic

Two-Levels of Logic Implementation of the Carry-Lookahead Block VLSI Arithmetic

Three-Levels of Logic Implementation of the Carry Block (restricted fan-in) VLSI Arithmetic

Three-Levels of Logic Implementation of the Carry Lookahead (restricted fan-in) VLSI Arithmetic

Delay Optimized CLA: Lee-Oklobdzija ‘91 Delay: Three-level BCLA Delay: Two-level BCLA VLSI Arithmetic

Delay Optimized CLA: Lee-Oklobdzija ‘91 (a.) 2-level BCLA D=8.5nS (b.) 3-level BCLA D=8.9nS VLSI Arithmetic

Motorola: CLA Implementation Example A. Naini, D. Bearden and W. Anderson, “A 4.5nS 96b CMOS Adder Design”, Proceedings of the IEEE Custom Integrated Circuits Conference, May 3-6, 1992. VLSI Arithmetic