ECE 3110: Introduction to Digital Systems Chapter 5 Combinational Logic Design Practices

180 likes | 350 Vues

ECE 3110: Introduction to Digital Systems Chapter 5 Combinational Logic Design Practices. Documentation Standards. Chapter Outline. Documentation Standards for digital systems. Digital Circuit Timing and Propagation delay

ECE 3110: Introduction to Digital Systems Chapter 5 Combinational Logic Design Practices

E N D

Presentation Transcript

ECE 3110: Introduction to Digital SystemsChapter 5Combinational Logic Design Practices Documentation Standards

Chapter Outline • Documentation Standards for digital systems. • Digital Circuit Timing and Propagation delay • Combinational Logic Design Structures :- Decoders- Encoders- Three-State Buffers- Multiplexers- Demultiplexers - EXCLUSIVE OR Gates and Parity Circuits- Comparators- Adders/ Subtracters- Arithmetic Logic Units ( ALUs)

Documentation Standards • Documentation of a digital system should provide the necessary information for building, testing ,operating , and maintaining the system. • Generally, documentation include: 1) A Specification describes what the circuit is supposed to do. 2) A block diagram showing the inputs, outputs, the main building blocks ( modules) of the system and how they are connected. 2) A schematic diagram showing all the components, their types, and all interconnections. 3) A timing diagram showing the logic signals as a function of time. 4) A structured logic frvice description showing the operation of the structures . For example, the function table of the multiplexer, or the program listing of a PLD ( Programmable Logic Device). 5) A Circuit description explaining of the operation of the logic circuit.

Block Diagram • A block diagram should show all inputs and outputs , the building blocks and their function names , and the data flow paths ( the logic signals).- The internal details of each block should not be shown.- Related logic signals are combined together and drawn with a double or heavy line, known as a bus • Example: Min/Max Circuit MIN/MAX X Comparator Y X>Y max(X,Y) Mux A bus is a collection of 2 or more related signal lines. Mux Z Mux min(X,Y)

Basic rules • A block diagram must show the most important system elements and how they work together. • Each block diagram should not be more than 1 page. • Large systems may require additional block diagrams of individual subsystems. (a top-level diagram shows the entire system. • Important control signals and buses should have names. • Flow of control and data should be clearly indicated. • Should not include internal details of each block (generally, NO gate symbols, NO pins).

Schematic Diagram • Details of component inputs, outputs, and interconnections • Reference designators • Pin numbers • Title blocks • Gate symbols • Signal names and active levels • Bubble-to-Bubble Logic Design • Layouts Logic diagram: an informal drawing without quite this level of detail.

DeMorgan equivalent symbols Which symbol to use? Answer depends on signal names and active levels.

Signal Names • Signal name: a descriptive alphanumeric label for each input/output signal. • In real system, well-chosen names convey information to readers • A signal name indicates • An action that is controlled (ENABLE, REQUEST, GO, PAUSE) • A condition that it detects such as READY_L, ERROR,… • Data that it carries, such as INBUS[31..0], ADDR[15…0]

Active Levels • Each signal name should have an active-level associated with it. A signal is active-high if it performs the named action or denotes the named condition when it’s HIGH or 1. A signal is active-low if it performs the named action or denotes the named condition when it’s LOW or 0. • The signal is asserted when it is in its active level and negated ( or deasserted ) when its not in its active level. • Different naming conventions for active levels available.

Naming conventions • Active low signal has a suffix of _Las part of the variable name. • Example :- ERROR is active high means there is an error when the signal is HIGH ( logic 1).- READY_L is active low means the data is ready when the signal is LOW ( logic 0).

Example LOW when error occurs Logic Circuit ERROR ERROR1_L HIGH when error occurs Logic Circuit ERROR ERROR_L

Signal name, logic expression, logic equation • A signal name is just a name, an alphanumeric label. • A logic expression combines signal names using switching algera operators (AND,OR,NOT). • A logic equation is an assignment of a logic expression to a signal name.Decribe one signal’s function in terms of other signals. • For example: READY_L, READY are signal names. READY’ is a logic expression. • Equation: DATA=ASEL.A+ASEL’.B Logic expression

Active Levels for Pins • When we draw the outline of a logic symbol, we think of the given logic function as occuring inside that outline. • In logic gates and logic structures the inversion bubble indicates the active level of the signal • Examples:- 2-to- 4 Decoder- EN_L is active low- A and B are active high- Y0_L, Y1_L, Y2_L,Y3_L are active low EN_L EN Y0 Y0_L Y1 Y1_L A A Y2 Y2_L B B Y3 Y3_L

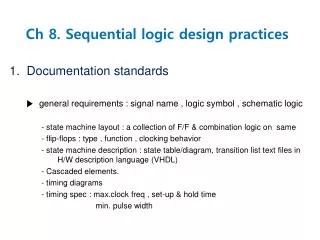

More ways of obtaining AND/OR functions (Generalized AND/OR function). • Four ways of AND function: output is asserted if both of its inputs are asserted. • AND gate (74x08): active-high input/output • NAND gate (74x00): active-high input, active-low output • NOR gate (74x02): active-low input, active-high output • OR gate (74x32): active-low input/output • Four ways of OR function: output is asserted if either of its inputs are asserted. • OR gate (74x32): active-high input/output • NOR gate (74x02): active-high input, active -low output • NAND gate(74x00): active-low inputs, active-high output • AND gate (74x08): active-low inputs/output

Next… • Bubble-to-Bubble logic design • Schematics • Drawing Layouts • Reading Wakerly CH-5.1-2