High Speed Pulse Generation Midterm Report

This report covers a research project on high-speed pulse generation for wireless connections, focusing on blind receiving algorithms. Two proposed solutions are discussed, highlighting advantages and disadvantages for each approach.

High Speed Pulse Generation Midterm Report

E N D

Presentation Transcript

High Speed Pulse GenerationMidterm Report Spring 2009 (Single Semester) By: Mironov Artiom Instructor: Yossi Hipsh

Overview • The current project is a part of large research, being performed by EE Technion faculty. • The research works on problems of wireless connections and implements new algorithm of blind receiving. • The receiver has no information about carrier signal (phase, frequency), but using special signal, as LO, manages to retrieve the modulated info signal.

Overview(cont.) • Symbolical Block Scheme of receiver shown in Pic. 1.1 • This special signal is periodic signal consisted of ones and zeros, for example as signal shown in Pic. 1.2 • Our goal is to produce this fast I-O pulse function used, as LO at mixer and to implement it in the suggested receiver. Pic. 1.1 Pic. 1.2

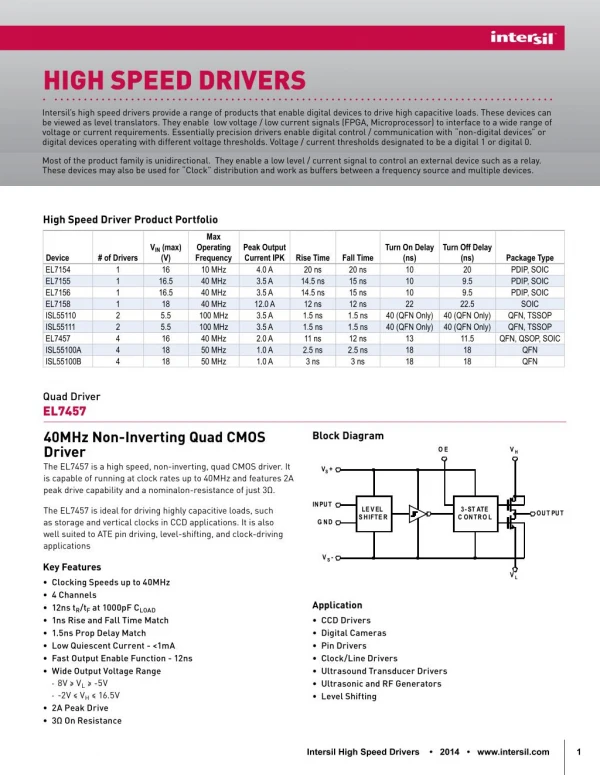

Input/output Scheme 8 bits 8 bits 1 0 1 1 0 . . . Pulse Generator Sequence Specifications Periodic Signal at 6GHz Power Supply +7V

Signal Specifications • High speed pulse signal at 6 GHz operating frequency. • The signal is periodic, consisted of 8 pulses. • Single bit is T=166 psec long. • Time pulse requirement 8 bits

Proposed Solution A • This solution was proposed at characterization report, however was slightly updated. • General Block Diagram: • Signal from sinus oscillator at 750 MHz proceeded through Limiter to achieve: Pic. 2 T=1.33 nsec 0.65 nsec

Proposed Solution A • The signal then splitted and one of the channels is delayed by 0.5 nsec, thus giving us the AND product: • The constructed signal is once more splitted to 8 and then used to construct pulse sequence, using logical gates and adjustable delays. CH1: d=0.5 ns CH2: T’=165ps AND:

Alternative Solution B • This solution uses sinus oscillator at 6 GHz frequency, to produce trigger signal for a shift register. • Shift register contains 8 bits of our pulse sequence, thus can produce needed periodic signal. • We use splitter at point 2, in order to have the ability to combine 2 sequences using OR gate at point 7. Fast limiter and technology matching unit used to achieve needed clock signal from 6 GHz sinus signal. Pic. 3

Solutions Comparison • Advantages and disadvantages of each solution : • In solution B we split the signal while it is single tone sinus, thus reducing the bandwidth , while in solution A we have to split pulse signal to 8, what requires very wide bandwidth and thus toughens our component selection. • Sequence determination and future possible changes in it, are much easier in Solution B, since made only by parallel load of shift register data, while requires precise delay calculation in Solution A. • Unfortunately we didn’t manage to find appropriate shift register in this frequency, so we chose solution A to be our final choice.

Gantt Chart Practical Work Finished Final Report Making Purchase Semi Report Char-ion Report