Digital Design with FPGAs: Examples and Resource Saving Tips Screen B

460 likes | 611 Vues

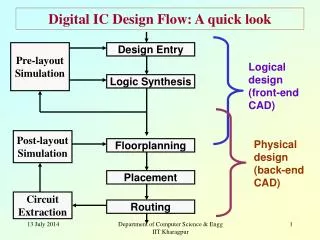

Digital Design with FPGAs: Examples and Resource Saving Tips Screen B. Wu, Jinyuan Fermilab IEEE NSS 2007 Refresher Course Oct, 2007. Indirect Cost of Complexity. If something like this can do the job…. … why do these?. Outline. Digital Design with FPGAs (This 45 min. Course)

Digital Design with FPGAs: Examples and Resource Saving Tips Screen B

E N D

Presentation Transcript

Digital Design with FPGAs:Examples and Resource Saving TipsScreen B Wu, Jinyuan Fermilab IEEE NSS 2007 Refresher Course Oct, 2007 IEEE NSS Refresher Course

Indirect Cost of Complexity If something like this can do the job… … why do these? IEEE NSS Refresher Course

Outline • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. IEEE NSS Refresher Course

“Any” 4-in Functions Full Adder CI A S B CO D D D D Q Q Q Q What Can Be Done With a Logic Element A B C D IEEE NSS Refresher Course

D Q ENA CLRN Xilinx Look-Up Table 16-bit Distributed RAM 16-bit Shift Register RAM16 SRL16 LUT4 4-input Look-Up Table IEEE NSS Refresher Course

D Q ENA CLRN Transistor Usage of Logic Element At least 96 transistors LUT 16-bit X 16 6-transistor RAM bit IEEE NSS Refresher Course

Full Adder CI A S D Q B CO D Q ENA CLRN Full Adder At least 96 transistors LUT 8-bit LUT 8-bit IEEE NSS Refresher Course

Transistor Counts IEEE NSS Refresher Course

TDC Using FPGA Logic Chain Delay • This scheme uses current FPGA technology • Low cost chip family can be used. (e.g. EP1K10QC208-2 $15.25) • Fine TDC precision can be implemented in slow devices (e.g., 0.4 ns in a 200 MHz chip). IN CLK IEEE NSS Refresher Course

Older Samples Selected Sample Q3 Selected Sample Q2 b0 Selected Sample Q1 Selected Sample Q0 SEL QF QE QD Newer Samples SEL=0 SEL=1 SEL=2 SEL=3 Edge Detection + Sample Selection IEEE NSS Refresher Course

ADC Test: Waveform Digitization on BD3_19 FPGA TDC TDC VREF 50 50 Input Waveform, Overlap Trigger & Reference Voltage 1000pF 100 Raw Data Converted IEEE NSS Refresher Course

83 12 31 47 28 71 65 55 23 46 91 19 72 16 44 87 12 16 19 23 Sorter Operation Sorter • Operation: • Initialization: All registers become 0xFF after DUMP=1 for at least 4 clock cycles. • Data Fetching: All data are clocked through and lowest four numbers are stored. • Dump: The lowest four numbers are output in sequence and all registers become 0xFF, i.e., initialized. • Warning: To keep all sorted data, do not use this circuit. Consider other schemes. IEEE NSS Refresher Course

Outline • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. IEEE NSS Refresher Course

D D Q Q ENA ENA CLRN CLRN LE Implementation of Registered Adder A1 LUT 8-bit LUT 8-bit B1 A2 LUT 8-bit LUT 8-bit B2 IEEE NSS Refresher Course

SCLR SLOAD D[] Q[] Inc/Dec CNTEN EN The Counter With Inc, Dec and Count Enable Controls, a Special Case of Accumulator 0: Disable +1: Inc -1: Dec D[] 0/+1/-1 A+B D[] Q[] B[] EN Don’t confuse the count enable CNTEN With clock enable EN. IEEE NSS Refresher Course

Decimations: With Integer ratios f S f D = f S / 6 Sample Interval = 6 IEEE NSS Refresher Course

A[] A>B A[] B[] == B[] LUT4 LUT4 LUT 8-bit LUT 8-bit LUT4 LUT4 LUT 8-bit LUT4 LUT4 LUT 8-bit LUT4 LUT4 Resource Usage of Comparators Equality Comparator A==B 0.5 LE/bit + Equality Comparator A==Constant 0.25 LE/bit + Magnitude Comparator A>B 1 LE/bit A B A B A A B A B IEEE NSS Refresher Course

Decimation With Non-integer ratios f S f D = f S / 6 f D = f S / 6.2 Sample Interval = 7 Sample Interval = 6 IEEE NSS Refresher Course

Duty-Cycle Based Single-Pin DAC DAC Input A A>B Counter B Q • The duty-cycle of the comparator output is proportional to the DAC input at port A. • Use external RC as low-pass filter. • Output voltage of an ideal LP filter is proportional to the DAC input. IEEE NSS Refresher Course

Exponential Sequence Generator if (CO==1) {Q = Q - Q/32;} S(-) SET D Q • An exponential sequence is generated using an accumulator shown above. • Note that not even one multiplier is used. • Other function sequences: sine, co-sine, tangent, co-tangent etc. can also be generated similarly. IEEE NSS Refresher Course

Outline • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. IEEE NSS Refresher Course

RAM RAM D Q D Q D Q D Q D Q D Q D Q D Q D Q D Q D WA WE D WA WE Q RA RE Q RA RE PUSH PUSH POP CNT CNT CNT -L Implementation of Pipeline and FIFO IEEE NSS Refresher Course

TS TS CM TDC T OUT FIFO PUSH DV Zero-Suppression IEEE NSS Refresher Course

Pipeline and FIFO IEEE NSS Refresher Course

TDC Data Concentration 48 Ch TDC/HRL TDC/HRL Zero Supp. L1 Buffer 1xM4K 16x256 TDC/HRL TDC/HRL Ch 4-7, TDC & L1 Buffer Ch 8-11, TDC & L1 Buffer Ch 12-15, TDC & L1 Buffer TDC/L1 Buffer/MUX Channels 16-31 EV Buffer & Truncating 16x128x2 TDC/L1 Buffer/MUX Channels 32-47 IEEE NSS Refresher Course

!P FA RAM DA AA WEA DB AB WEB QA QB P CNT MA Ping-Pong Paged RAM • P==0 • MPU accesses page 0 • FPGA accesses page 1 • P==1 • MPU accesses page 1 • FPGA accesses page 0 FA AA[9]=!P P FA UPDATA AB[9]=P MA MA MPU IEEE NSS Refresher Course

FPGA RAM Aspect Ratio IEEE NSS Refresher Course

Each Address Line: Doubles RAM Size. 256 Words 256 Words 8 address lines 8+8 address lines 256 Words 256 Words 256 Words 9 address lines IEEE NSS Refresher Course

High Precision 2^N LUT A B C ROM LUT 28=256 w ROM LUT 28=256 w 0.6931471 Constant Multiplication, May use LUT 2(A) 2(B) X X 1+ X (32-bit Precision) 2(A+B+C) = 2(A) * 2(B) *(1+(ln2)*C) IEEE NSS Refresher Course

Outline • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. IEEE NSS Refresher Course

Histogram Booking K RA,WA +1 IEEE NSS Refresher Course

D Q D Q D Q D Q D Q RAM D WA WE RA Q Read-After-Write (RAW) Hazard K4 K1 K2 K1 K0 DV Wrong! Wanted to be N1+1 +1 N1 IEEE NSS Refresher Course

K1 K2 D Q D Q D Q D Q D Q DV2 DV1 K1==K2 RAM D WA WE RA Q RAW Hazard Prevention: Instruction Merging If a bin is hit several times, they are combined in a single accumulation instruction. K DV &&== &&== &&== +1+N IEEE NSS Refresher Course

Histogram Fast Reset K • Keep a run counter RC that ++ for each reset. • Assign an Index RAM that has same number of bins as the Content RAM. • When a bin is hit, the Index RAM is first readout (to MR) and then written with current RC. • If MR!=RC, the bin is to be reset. • If MR==RC, the bin is to be +1. Content RAM RA,WA 0 +1 MR!=RC Old run RC CE == MR==RC Current run RC Reset MR Index RAM IEEE NSS Refresher Course

Prevent Index RAM from Rolling Over K • The RC/Index RAM have limited bits that may cause roll-over (millennium-bug). • E.g. RC=1, =513, =1025 look same with 9-bit RC. • To prevent roll-over, write a bin of Index RAM with RC in rotational address at each reset. • For a 256-bin histogram, the contents in Index RAM will be always RC-256 or newer. Content RAM RA,WA 0 +1 MR!=RC Old run RC CE == MR==RC Current run RC Reset MR Index RAM A(RC) IEEE NSS Refresher Course

Outline • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. IEEE NSS Refresher Course

Multipliers in Cyclone II Multiplier 18-bit x 18-bit IEEE NSS Refresher Course

Approximation is OK 8-bit Square X=256-511 X ^2 X2 & FF00&X2 00 sqrt Y |Y-X|<0.5 INT(Y+0.5)=X IEEE NSS Refresher Course

Replacing Multiplication With Addition A 0 0 +) A 5*A A 0 0 0 0 0 0 0 0 -) A 0 0 0 248*A IEEE NSS Refresher Course

Outline • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. IEEE NSS Refresher Course

Relative Errors of Several Track Fitter Schemes Multiplier-less FPGA LS Fitter Least Square Fitter IEEE NSS Refresher Course

Coefficient Table, Least Square Fitter IEEE NSS Refresher Course

Coefficient Table, ML Fitter IEEE NSS Refresher Course

Fitting Errors From Approximations …increases fitting error by only 2%. 20% approximation in coefficients … IEEE NSS Refresher Course

Additional Courses on FPGA Applications • Digital Design with FPGAs (This 45 min. Course) • Logic Element in a Nutshell • Variations of the Registered Adders • Tricks of Using RAM • RAM based histograms • Topics on Multipliers • Curved Track Fitter • Advanced Topics on FPGA Applications (Included as Supplemental Materials) • Doublet Finding, Hash Sorter • Triplet Finding, Tiny Triplet Finder (TTF) • Options of Sequence Control, Recursive Structure, etc. • Reconfigurable Computing with FPGA (Planned) IEEE NSS Refresher Course

The End Thank you IEEE NSS Refresher Course