Course web page:

ECE 545 Digital System Design with VHDL. Course web page:. ECE web page Courses Course web pages ECE 545. http://ece.gmu.edu/coursewebpages/ECE/ECE545/F09/. Kris Gaj. Research and teaching interests: reconfigurable computing computer arithmetic cryptography network security

Course web page:

E N D

Presentation Transcript

ECE 545 Digital System Design with VHDL Course web page: ECE web page Courses Course web pages ECE 545 http://ece.gmu.edu/coursewebpages/ECE/ECE545/F09/

Kris Gaj • Research and teaching interests: • reconfigurable computing • computer arithmetic • cryptography • network security • Contact: • The Engineering Building, room 3225 • kgaj@gmu.edu Office hours: Monday, Tuesday, Wednesday6:00-7:00 PM

ECE 545 Part of: MS in Computer Engineering Required course in two concentration areas: Digital Systems Design Microprocessor and Embedded Systems Elective course in the remaining concentration areas MS in Electrical Engineering Elective

Courses Design level Computer Arithmetic VLSI Design for ASICs VLSI Test Concepts Digital System Design with VHDL algorithmic ECE 645 ECE 545 register-transfer ECE 682 ECE 681 gate ECE 586 Digital Integrated Circuits transistor ECE 680 PhysicalVLSI Design layout Semiconductor Device Fundamentals MOS Device Electronics ECE 584 ECE684 devices

DIGITAL SYSTEMS DESIGN • Concentration advisors:Kris Gaj, Ken Hintz • ECE 545 Digital System Design with VHDL– K. Gaj, project, FPGA design with VHDL, • Aldec/Synplicity/Xilinx • 2. ECE 645 Computer Arithmetic– K. Gaj, project, FPGA design with VHDL or Verilog, • Aldec/Synplicity/Xilinx • 3. ECE 681 VLSI Design for ASICs– N. Klimavicz, project/lab, back-end ASIC design with Synopsys tools • 4. ECE 586 Digital Integrated Circuits – D. Ioannou, R. Mulpuri • 5. ECE 682 VLSI Test Concepts • – T. Storey

Grading Scheme • Homework - 10% • Project - 40% • Midterm Exam - 20% • Final Exam - 30%

Midterm exam 1 • 2 hours 30 minutes • in class • design-oriented • open-books, open-notes • practice exams will be available on the web Tentative date: Thursday, October 21st

Final exam • 2 hours 45 minutes • in class • design-oriented • open-books, open-notes • practice exams will be available on the web Date: Wednesday, December 16, 7:30-10:15pm

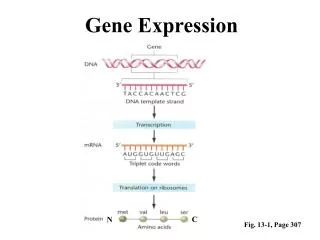

Hash Function arbitrary length m message hash function h It is computationally infeasible to find such m and m’ that h(m)=h(m’) h(m) hash value fixed length

Main Application: Digital Signature Signature HANDWRITTEN DIGITAL A6E3891F2939E38C745B 25289896CA345BEF5349 245CBA653448E349EA47 • unique identification • proof of agreement to the contents • of the document Main Goals:

Typical Digital Signature Scheme Alice Bob Signature Message Signature Message Hash function Hash function Hash value 1 Hash value yes no Hash value 2 Public key cipher Public key cipher Alice’s public key Alice’s private key

Handwritten and Digital Signatures Common Features Digital signature Handwritten signature 1. Unique 2. Impossible to be forged 3. Impossible to be denied by the author 4. Easy to verify by an independent judge 5. Easy to generate

Handwritten and Digital Signatures Differences Digital signature Handwritten signature 6. Associated physically with the document 7. Almost identical for all documents 8. Usually at the last page 6. Can be stored and transmitted independently of the document 7. Function of the document 8. Covers the entire document

Cryptographic Standards So how the cryptographic standards have been created so far?

NSA National Security Agency (also known as “No Such Agency” or “Never Say Anything”) Created in 1952 by president Truman Goals: • designing strong ciphers (to protect U.S. communications) • breaking ciphers (to listen to non-U.S. communications) Budget and number of employees kept secret Largest employer of mathematicians in the world Larger purchaser of computer hardware

NSA-developed Cryptographic Standards Block Ciphers 2005 1999 1977 DES – Data Encryption Standard Triple DES 1995 2003 1993 Hash Functions SHA-1–Secure Hash Algorithm SHA-2 SHA-0 2000 1970 1990 1980 2010 time

Cryptographic Standard Contests IX.1997 X.2000 AES 15 block ciphers 1 winner NESSIE I.2000 XII.2002 CRYPTREC V.2008 XI.2004 34 stream ciphers 4 SW+4 HW winners eSTREAM XII.2012 X.2007 51 hash functions 1 winner SHA-3 96 97 98 99 00 01 02 03 04 05 06 07 08 09 10 11 12 time

Criteria used to evaluate cryptographic transformations Security Hardware Efficiency Software Efficiency Flexibility

Software or hardware? HARDWARE SOFTWARE security of data during transmission speed random key generation access control to keys low cost resistance to side-channel attacks flexibility (new cryptoalgorithms, protection against new attacks) tamper resistance

Primary efficiency indicators Hardware Software Area Speed Speed Memory Memory Power consumption

Efficiency parameters Latency Throughput = Speed Mi+2 Mi Mi+1 Mi Time to encrypt/decrypt a single block of data Encryption/ decryption Encryption/ decryption Number of bits encrypted/decrypted in a unit of time Ci+2 Ci Ci+1 Ci Block_size · Number_of_blocks_processed_simultaneously Throughput = Latency

Advanced Encryption Standard (AES) Contest 1997-2001 June 1998 Round 1 15 Candidates from USA, Canada, Belgium, France, Germany, Norway, UK, Israel, Korea, Japan, Australia, Costa Rica Security Software efficiency Flexibility August 1999 Round 2 5 final candidates Security Mars, RC6, Rijndael, Serpent, Twofish Hardware efficiency October 2000 1 winner: Rijndael Belgium

Speed of the final AES candidates in Xilinx FPGAs K.Gaj, P. Chodowiec, AES3, April, 2000 Speed [Mbit/s] 500 450 400 350 300 250 200 150 100 50 0 Mars RC6 Serpent Rijndael Twofish

Survey filled by 167 participants of the Third AES Conference, April 2000 # votes 100 90 80 70 60 50 40 30 20 10 0 Mars RC6 Rijndael Serpent Twofish

Results of the NSA group ASICs Speed [Mbit/s] AES3, April, 2000 700 NSA ASIC GMU FPGA 606 600 500 431 414 400 300 202 177 200 143 105 103 61 100 57 0 RC6 Twofish Mars Rijndael Serpent

Efficiency in software: NIST-specified platform 200 MHz Pentium Pro, Borland C++ Speed [Mbits/s] 128-bit key 192-bit key 256-bit key 30 25 20 15 10 5 0 Mars Rijndael Serpent RC6 Twofish

NIST Report: Security AES Final Report, October 2000 Security MARS High Serpent Twofish Rijndael Adequate RC6 Simple Complex Complexity

eSTREAM Stream Cipher Comparison • Part of the GMU Fall 2006 & Fall 2007 graduate courses • ECE 545 Introduction to VHDL • Individual 6-week project • 4 students working independently on each eSTREAM cipher • best code for each algorithm selected at the end • of the semester • selected designs verified and revised in order to assure • correct functionality • standard interface & control • possibly uniform design & coding style

Comparison of 4 Focus Hardware-Oriented Stream Ciphers FPGA: Xilinx Spartan 3 family Throughput [Mbit/s] Best T64 12000 10000 Trivium 8000 T32 6000 4000 T16 G16 Phelix 2000 Grain AES G1 Worst Mickey-128 0 Area [CLB slices] 0 200 400 600 800 1000 1200 1400

Comparison of 8 Final Candidates Sorted by Minimum Area and Maximum Throughput/Area

Conclusions from the Comparisonof the eSTREAM Candidates in Hardware Very large differences among 8 leading candidates: ~30 x in terms of area (Grain v1 vs. Edon80) ~500 x in terms of the throughput to area ratio (Trivium (x64) vs. Pomaranch)

Your Project • 14 SHA-3 candidates left in the contest • Given: • specification of the function • reference implementation in C • interface • testbench (without test vectors) • Generate: • synthesizable code in VHDL • results for Xilinx FPGAs • optimized versions of the code • results for multiple families of FPGAs

All Projects - Organization • Projects divided into phases • Deliverables for each phase submitted through Blackboard at selected checkpoints and evaluated by the instructor and/or TA • Feedback provided to students on a best effort basis • Final report and codes submitted using Blackboard at the end of the semester

Honor Code Rules • All students are expected to write and debug their codes individually • Students are encouraged to help and support each other in all problems related to the- operation of the CAD tools,- basic understanding of the problem.

Course Objectives • At the end of this course you should be able to: • Code in VHDL for synthesis • Decompose a digital system into a controller (FSM) and datapath, and code accordingly • Write VHDL testbenches • Synthesize and implement digital systems on FPGAs • Understand behavioral, non-synthesizable VHDL and its role in modern design • Effectively code digital systems for cryptography, signal processing, and microprocessor applications • This knowledge will come about through homework, exams, and an extensive project • The project in particular will help you know VHDL and the FPGA design flow from beginning to end

Hands-On Sessions Wednesday, September 9, 2009 The Engineering Building, Room 3204 Group 1: 4:30-7:10pm Group 2: 7:20-10:00pm