Multiple Chip Planning for Chip-Interposer Codesign

Multiple Chip Planning for Chip-Interposer Codesign. Yuan-Kai Ho and Yao-Wen Chang Department of EE, NTU, Taiwan. DAC 2013. Outline. Introduction Preliminaries Problem Formulation Review of B*-tree Proposed Algorithm Experimental Results Conclusions. Introduction.

Multiple Chip Planning for Chip-Interposer Codesign

E N D

Presentation Transcript

Multiple Chip Planning for Chip-Interposer Codesign Yuan-Kai Ho and Yao-Wen Chang Department of EE, NTU, Taiwan. DAC 2013

Outline • Introduction • Preliminaries • Problem Formulation • Review of B*-tree • Proposed Algorithm • Experimental Results • Conclusions

Introduction • As technology advances, interposer-based 3D ICs(2.5D ICs) become one of the most promising solutions for enhancing system performance and supporting heterogeneous integration.

Introduction • To improve the inter-chip routing quality, it is desirable to simultaneously consider a silicon interposer and multiple chips mounted on it.

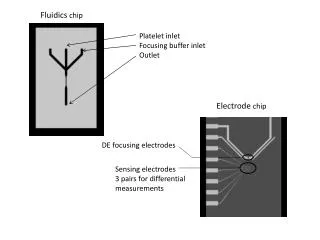

Preliminaries • Problem Formulation • Given: • A set of chips mounted on a interposer • A set of macros in each chip • A set of I/O buffers in each chip • A set of micro bumps in each chip • Objective: • Place macros and I/O buffers within corresponding chips without any overlaps • Find the locations of the chips on the interposer • Minimize the total wirelength

HB*-tree Construction • To reduce the wirelength between I/O buffers and macros, cluster a macro and its connected I/O buffers into a group.

HB*-tree Construction • An HB*-tree is a three-level hierarchical B*-tree. • First level is the interposer level. • Second level is the chip level. • Third level is the group level.

HB*-tree Perturbation • To perturb an HB*-tree in SA, apply the following operations: • Op1: Rotate a chip, a macro, an I/O buffer, or a macro-buffer group. • Op2: Move a node of a subtree to another place of the same subtree. • Op3: Swap two nodes within a subtree.

Cost Function Evaluation • Define the cost function of a placement P as follows: • A: total area of chips • W1: total WL of inter-chip connections • W2: total WL of intra-chip connections • R0: current aspect ratio of all chips • R0*: pre-defined aspect ratio of all chips • Ri: current aspect ratio of the chip i • Ri*: pre-defined aspect ratio of the chip i

Micro Bump Assignment • Bipartite matching to establish the connections between I/O buffers and micro bumps.

Conclusions • This paper proposed a multiple chip planning algorithm for chip-interposer codesign problem. • Experimental results have shown that the approach is effective and efficient for chip-interposer codesign problem.