History-Based VLSI Legalization via Network Flow: Innovations and Results

180 likes | 295 Vues

This paper presents a novel approach to VLSI layout legalization utilizing a history-based multi-commodity min-cost flow (MCMF) formulation. It effectively reduces overlaps and maintains design integrity during placement on integrated circuits. The proposed algorithm dynamically optimizes gate positions, integrating historical data for improved performance. We outline the problem formulation, present our efficient techniques, and discuss experimental results that benchmark our approach against existing solutions. Our findings illustrate a significant enhancement in quality of results (QoR) compared to traditional methods.

History-Based VLSI Legalization via Network Flow: Innovations and Results

E N D

Presentation Transcript

History-based VLSI Legalization using Network Flow Minsik Cho, HaoxingRen, Hua Xiang, RuchirPuri DAC’10

Outline • Introduction & Contribution • Problem Formulation • Algorithm • Network Flow Formulation • Flow Realization • Region Placement • History Learning • Experimental Results • Conclusion & Future Work

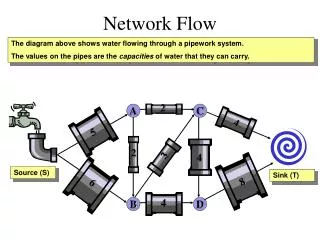

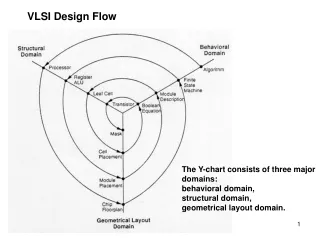

Introduction • The high density of design in a chip affects the entire physical design. • Take care of placement can reduce the complexity of the following stages: • buffering, gate sizing, routing, etc. • The main goal of placement • Locate all the objects without overlap • Satisfying each kinds of design objectives. • Legalization is an important step between global and detail placement to remove all the overlaps with minimum perturbation or impaction.

Contribution • A novel gate-centric MCMF formulation • Optimize the deviation for each gate better • History scheme can be integrated smoothly • Incorporate a history-based technique into a new network flow formulation • Propose efficient techniques to realize a flow into gate movements based on a Subset-sum problem

Problem Formulations • A rectangle chip is partitioned into equal-sized circuit rows, and each row is further divided into block-free regions. • The Manhattan distance between these two positions is defined as deviation

Problem Formulations (cont) Maximum deviation Average weighted sum

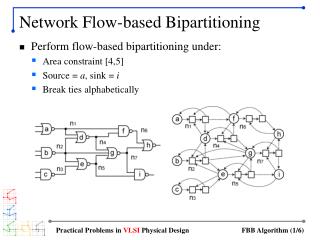

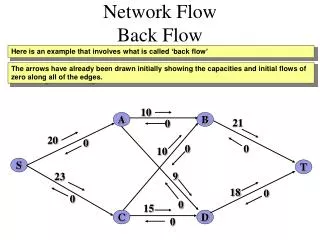

Further Issues • Base on network flow, how to set the sources and sinks by this formula? • Set all the gates in one of overflow regions as sources, other regions as sinks. • How to solve that general network flow cannot model discrete sizes of gates? • Using unbounded or maximum width size of gate as limit of flow and do the Flow Realization. • How to calculate the deviation of the y-value? • Using the center Yr+Wr/2 to evaluate the deviation, and do the Region Placement.

Step 1: Network Flow Might move partially Times of history failed

Step 2: Flow Realization • There is a partial flow from A to the empty space • Solve Subset-sum problem(NP class) • Partition into two set and fit the regions with cheapest solution. • We set the size solution T < λ • Control the bounded flow and λcan reduce run time. • It returns Failure if the problemis unsolvable.

Step 3: Region Placement • Find y-value of all gates in a region for minimum deviation is NP-Hard. • Order the gates according to the center location (xi, yi+wi/2) rather than (xi, yi), and it provides the less deviation according to experience. • In case of overflow region, we temporarily scale down wi with Wr/Or, just make placement fesiable. • Solve this problem by single row placement refer to [3,4,7, 11].

Step 4: History Learning • To avoid unrealizable flow, increasing the history factor h[wi][r][p] for the cost expensive enough. Success flow onthe 5th iteration

Post-Optimization & Speedup • When we get a legal solution, it is possible that some gates have large deviation. • Greedily move gates toward their initial position. • Using Flow Realization with zero flow • The complexity of network flow is: • Boundle tightly coupled gates if the total width less than maximum width in library, it can reduce |I| effectively. • In most case, a gate migrates to the nearby regions, we caninsert the edges by user defined. (reduce |E|) • Using hierarchical approach to reduce |R|.

Experiment Results • Environment • Implement in C++ • 2.4GHz Linux machine with 4G RAM • Competitor • NTUPlace3-LE, FastPlace3, Dragon2006, BonnL • Benchmark • 45nm with mixed-sized blockages and fixed gates • From the industrial global placer • Ignore • Wire length optimization

Experiment Results (cont) • Failure rate comparison

Experiment Result (cont) • Compare QoR with NTUPlace

Conclusion & Future Work • Using History-based MCMF to solve the general problems cannot solve by normal MCMF. • Simultaneously legalization often get better QoR. • Using the history-based technique • The assignment problem with the in-flow of a souce more than one. • The cost of SA-based problem. • By solving the Subset-sum problem • We can solve network flow out of bound to get more optimization chances.