Optimizing L1CTT Track Reconstruction: Geometry, Efficiency, and Dead Time Management

This document outlines the goals and methodologies for enhancing L1CTT track reconstruction, focusing on the use of SMT hits and the remapping of CFT geometry to improve detection efficiency. Key parameters, such as fixed road width and selective timing, are adjusted for optimal performance within a budgeted dead time of ~50 µs. The approach includes cluster correction, queuing simulation, and a detailed evaluation of input rates in a no-buffering scenario. The study aims to minimize loss in efficiency while increasing the accuracy of track finding in high-energy physics environments.

Optimizing L1CTT Track Reconstruction: Geometry, Efficiency, and Dead Time Management

E N D

Presentation Transcript

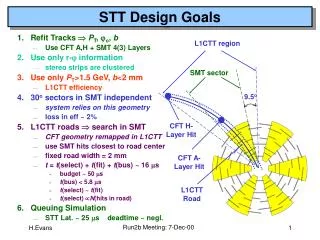

STT Design Goals • Refit Tracks PT, o, b • Use CFT A,H + SMT 4(3) Layers • Use only r- information • stereo strips are clustered • Use only PT>1.5 GeV, b<2 mm • L1CTT efficiency • 30o sectors in SMT independent • system relies on this geometry • loss in eff ~ 2% • L1CTT roads search in SMT • CFT geometry remapped in L1CTT • use SMT hits closest to road center • fixed road width = 2 mm • t = t(select) + t(fit) + t(bus) ~ 16 s • budget ~ 50 s • t(bus) < 5.8 s • t(select) ~ t(fit) • t(select) N(hits in road) • Queuing Simulation • STT Lat. ~ 25 s deadtime ~ negl. L1CTT region SMT sector 9.5o CFT H-Layer Hit CFT A-Layer Hit L1CTT Road Run2b Meeting: 7-Dec-00

correct & cluster correct & cluster STT Functionally L1CTT Tracks FRC broadcast Trig/Road data SMT Data (2 HDI / fiber) Trigger (SCL) at input rate (no buffering) 1 / input roads<46 / 60o clusters coord transf compare clst / rd compare clst / rd 1 / road clusters in roads STC fit matrix LUT TFC coord transf fit 8 dsp / 30o fit L2CTT fitted tracks Run2b Meeting: 7-Dec-00

CPU spare spare VBD spare spare terminator TFC STC STC STC STC STC FRC STC STC STC STC TFC spare terminator 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 Sector 1 Sector 2 STT Architecture Run2b Meeting: 7-Dec-00