Overview of Floating Point Adder Design and Simulation Using Verilog and Icarus Verilog

This document provides a comprehensive review of floating point adder design, focusing on gate-level diagrams and Verilog module implementations. It covers the process of simulating Verilog files using Icarus Verilog, detailing both compilation and execution steps. Key topics include the representation of floating point numbers, adder circuit construction, and the usage of Icarus Verilog tools like `iverilog` for compilation and `vvp` for runtime execution. Understanding floating point representation is crucial for handling a wide range of numerical values in computer systems.

Overview of Floating Point Adder Design and Simulation Using Verilog and Icarus Verilog

E N D

Presentation Transcript

Review • Adder gate level diagram • Adder Verilog module • Processing Verilog files using Icarus Verilog • Simulation verilog module definition using vvp • Floating point representation

Adder Circuit • Adder (a,b,cin) s, cout • s = ? • cout = ?

Processing Verilog File • IcarusVerilog, vvp are the tools available on cse machines • IcarusVerilog compiler: iverilog • iverilog is a compiler that translates Verilog source code into executable programs for simulation, or other netlist formats for further processing. The currently supported targets are vvp for simulation • vvp is the run time engine that executes the default compiled form generated by IcarusVerilog. The output from the iverilog command is not by itself executable on any plat form. Instead, the vvp program is invoked to execute the generated output file.

Using the Verilog Compiler and Runtime • Design your Verilog module according to the specification given • For adder, lets say we have saved the verilog module design in “adder.v” • Compile the module definition into a form that can be executed by vvp runtime. • iverilog -o adder adder.v • Output of iverilog command is stored in file “adder” • Run the code to check the output, that is typically generated by the tester code. • vvp adder • You will see the output on the screen • You can also capture into a file to submit it or print it.

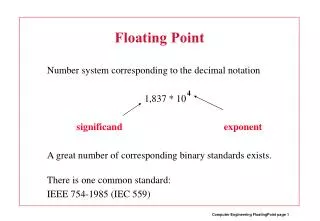

Floating point numbers • Why do we need them? • To represent very large number and very small number. • To represent a larger range of number with a given size in bits. • Consider a 4 bit container • Consider a 8 bit container • Examples: An astronautical unit (Au)is the distance between the earth and the sun in meters. • 150,000,000,000 meters • Size of Helium atom: 1 angstrom: 10-10 meters • See more details on units of measurement here

FP Representation S Exponent Fraction Value = (-1)S X F X 2 E 32 bit single precision 64 bit double precision IEEE 754 format

FP Addition and Multiplication • Components: operands, ALU, control, comparison, shifters, normalize, round • Control • ALUs • Figures: 3.17, 3.16, 3.18