Understanding Testbenches in Verilog: Basics to Advanced Concepts

50 likes | 182 Vues

This comprehensive guide covers the fundamentals of testbenches in Verilog, a crucial aspect of hardware simulation. It delves into the structure of non-synthesizable testbenches, emphasizing four-value logic, delays, and initial blocks. The document explains how to instantiate devices under test (DUT), manage input signals, and sample outputs effectively. Additionally, it explores the practical use of non-synthesizable registers and the importance of delays in simulations. With insights into Verilog's versatility and its applications in simulation, this resource serves as a valuable reference for designers and engineers.

Understanding Testbenches in Verilog: Basics to Advanced Concepts

E N D

Presentation Transcript

Testbench Basics • Testbench Form • Four Value Logic • Delays • Initial blocks • tasks • clocks • Simultaneous switching • First Lab problem

Simple Testbench Form • Testbench • Top level of simulation • Instantiates all devices under test Testbench (non-synthesizable) registers • Registers • Drive DUT inputs • Hold state unless changed • Non-synthesizable registers settable at any time Device under test (synthesizable) • Wires • sample DUT outputs • DUT changes wire outputs in response to inputs Non-synthesizable Verilog has more flexibility in simulation than Synthesizable Verilog! wires

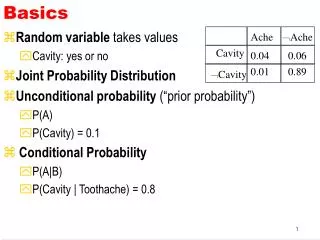

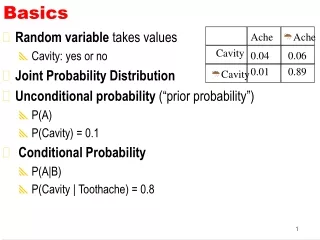

Four Value Logic • Verilog Logic Values • any bit to has one of four values • 1, 0, x (unknown), z (high impedance) • z — the high impedance output of a tri-state gate. • How do they map to reality? • 0, 1 … obvious • z … A tri-state gate is high impedance (z) when not driving 0 or 1. • This allows other gates to drive the same wire. • Not used much on-chip. Real important between chips to save I/O connections • x … Simulators start all values as unknown (x). No real gate drives x onto a wire. • x is a great simulation debugging aid.

Modeling Delays assign #5 inertial = a; //schedule eval & assign in 5 ns assign transport = #5 a; //eval now and assign in 5 ns 10ns 2ns a inertial transport Bad idea for design because delays are ignored by synthesizer - no accurate delay elements in chips - real delay depends on place, route & technology Essential for testbenches because designs are simulated with no delay - inertial delay approximates gates - transport delay approximates wires

Why is Verilog so general? • It was invented several years before synthesis • Intended for design simulation and architecture modeling • Non-synthesizable Verilog is very useful for testbenches • Non-synthesizable Verilog is very useful for external component modeling • Analog constructs exist but are too simple for simulation • There are better tools for architectural modeling