Memory Organization and Segmentation

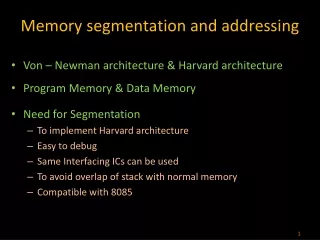

Memory Organization and Segmentation. Introduction. Memory is divided into bytes, words and dwords Words are stored in two consecutive bytes and dwords in 4 consecutive bytes It supports larger units of memory: pages and segments.

Memory Organization and Segmentation

E N D

Presentation Transcript

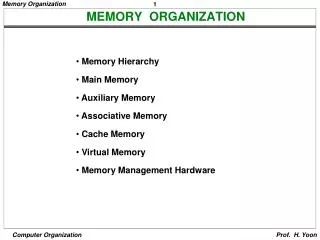

Introduction • Memory is divided into bytes, words and dwords • Words are stored in two consecutive bytes and dwords in 4 consecutive bytes • It supports larger units of memory: pages and segments. • Segmentation: Memory is divided into one or more variable length segments which can be swapped to disk or shared between programs.

Introduction • Paging: Memory is organized into one or more 4KB pages. • Segmentation and Paging can be combined to gain advantages of both systems. • Segmentation is used for organizing memory in logical modules • Pages are useful for system programmer for managing physical memory of system.

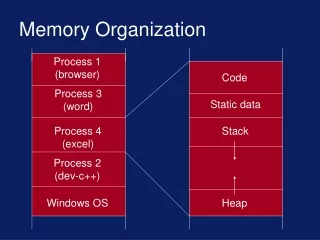

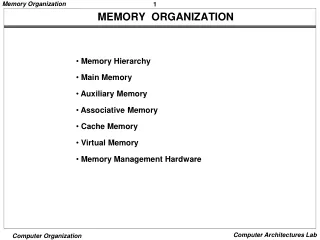

Address Spaces • 80386DX has three distinct address spaces: • Logical(Virtual) Address: • It consists of a selector and an offset • Selector : contents of segment register • Offset : Effective address (sum of base, index and displacement) • Each task has maximum of 16K selectors (214) and offset can be 4GB(232) to give a total of 246 or 64TB

Address Spaces • Linear Address • Segmentation unit translates logical address space into 32-bit linear address space. • If there is no paging linear address will be the physical address • Physical Address • Paging unit translates linear address space to physical address space • It is what appears on address pins.

Operating Modes UQ: State and explain the operating modes of X86 family of processors. Show the mode transition diagram highlighting important features.(10 Marks)

Operating Modes • The Intel 386DX has two modes of operation • Real Mode (Real Address) and • Protected Mode (Protected Virtual Address Mode) • Real Mode: • It works as a very fast 8086 with 32-bit extensions. • It is required to set up the processor for protected mode

Operating Modes • Protected Mode: • It provides access to sophisticated memory management, paging and privilege capabilities of the processor

Real Mode Architecture • It has same base architecture as 8086 • When a processor is reset, it is initialized in real mode. • It sets up the processor for Protected Mode. • The segment size of 80386 in real mode is 64KB • The maximum memory size is 1MB • Only address lines A2-A19 are active

Real Mode Architecture • Paging is not allowed in real mode and hence the physical address is same as linear. • Physical Address is formed by adding contents of segment register shifted left by 4 bits to an effective address. • This results in a physical address from 00000000 to 0010FFEF (FFFF0+FFFF) • Real mode segments always start on 16-byte boundaries since they are left shifted.

Real Mode Architecture • All segments in Real Mode are exactly 64KB long and generate exception 13 if a data operand or instruction fetch occurs past the end of a segment. • Segments may be overlapped in Real Mode.If a particular segment does not use all 64KB another segment can be overlayed on top of the unused portion of the previous segment.

Protected Mode UQs : Draw protected mode address translation mechanism of 80386 and explain segment translation in detail.(2)

Protected Mode Architecture • It increases linear address space to 4GB and virtual address space to 64TB • This mode uses two components to form the logical address: • 16 bit selector: to determine the linear base address of the segment • 32 bit offset: Added to base address to form the linear address

Protected Mode: Addressing Mechanism • In this mode, the selector is used to specify an index to the operating system defined table • The table contains the 32-bit base address of a given segment. • The linear address is formed by adding base address to the offset

Protected Mode: Addressing Mechanism • Paging provides a means of managing very large segments. • It translates linear address into physical address.