MOSFET 及相关器件

现代半导体器件物理与工艺. Physics Technology of Modern Semiconductor Devices. MOSFET 及相关器件. 2004,7,30. 本章内容. MOS 二极管 MOSFET 基本原理 MOSFET 按比例缩小 CMOS 与双极型 CMOS 绝缘层上 MOSFET MOS 存储器结构 功率 MOSFET. MOS 二极管.

MOSFET 及相关器件

E N D

Presentation Transcript

现代半导体器件物理与工艺 Physics Technology of Modern Semiconductor Devices MOSFET及相关器件 2004,7,30

本章内容 • MOS二极管 • MOSFET基本原理 • MOSFET按比例缩小 • CMOS与双极型CMOS • 绝缘层上MOSFET • MOS存储器结构 • 功率MOSFET

MOS二极管 MOS二极管在半导体器件物理中占有极其重要的地位,因为它是研究半导体表面特性最有用的器件之一.在实际应用中,MOS二极管是先进集成电路中最重要的MOSFET器件的枢纽.在集成电路中,MOS二极管亦可作为一储存电容器,并且是电荷耦合器件(CCD)的基本组成部分 理想MOS二极管 MOS二极管的透视结构如图(a)所示.图(b)为其剖面结构,其中d为氧化层的厚度,而V为施加于金属平板上的电压.当金属平板相对于欧姆接触为正偏压时,V为正值;而当金属平板相对于欧姆接触为负偏压时,V为负值.

MOS二极管 右图为V=0时,理想p型MOS二极管的能带图.功函数为费米能级与真空能级之间的能量差(金属:qm;半导体:qs),qχ为电子亲和力,即半导体中导带边缘与真空能级的差值,qΨB为费米能级EF与本征费米能级Ei的能级差. 理想MOS二极管定义为: (1)在零偏压时,金属功函数qm与半导体功函数qs的能级差为零或功函数差qms为零,如下式.即在无外加偏压之下其能带是平的(称为平带状况). (2)在任意的偏压之下,二极管中的电荷仅位于半导体之中,且与邻近氧化层的金属表面电荷量大小相等,但极性相反; (3)在直流偏压下,无载流子通过氧化层,亦即氧化层的电阻值为无穷大 。

MOS二极管 当一理想MOS二极管偏压为正或负时,半导体表面可能会出现三种状况.对p型半导体而言,当一负电压施加于金属平板上时,SiO2-Si界面处将产生超量的空穴,接近半导体表面的能带将向上弯曲,如图.对理想MOS二极管而言,不论外加电压为多少,器件内部均无电流流动,所以半导体内部的费米能级将维持为一常数.在半导体内部的载流子密度与能级差成指数关系,即 半导体表面向上弯曲的能带使得的能级差EF-Ei变大,进而提升空穴的浓度,而在氧化层与半导体的界面处产生空穴堆积,称为积累现象。其相对应的电荷分布如图所示.

MOS二极管 当外加一小量正电压于理想MOS二极管时,靠近半导体表面的能带将向下弯曲,使EF=Ei,形成多数载流子(空穴)耗尽,称为耗尽现象。在半导体中单位面积的空间电荷Qsc的值为qNAW,其中W为表面耗尽区的宽度. 当外加一更大的正电压时,能带向下弯曲得更严重.使得表面的本征能级Ei越过费米能级EF,如图。正栅极电压将在SiO2-Si的界面处吸引更多的负载流子(电子).半导体中电子的浓度与能差EF-Ei成指数关系,即

MOS二极管 由于EF-Ei>0,在半导体表面上的电子浓度将大于ni,而空穴浓度将小于ni,即表面的电子(少数载流子)数目大于空穴(多数载流子),表面载流子呈现反型,称为反型现象. 起初,因电子浓度较小,表面处于一弱反型的状态,当能带持续弯曲,使得导带的边缘接近费米能级.当靠近SiO-Si由界面的电子浓度等于衬底的掺杂量时,开始产生强反型.在此之后,大部分在半导体中额外的负电荷是由电子在很窄的n型反型层(0≤x≤xi)中产生的电荷Qn[如图]所组成,其中xi为反型层的宽度.xi典型值的范围从1nm~ 10nm,且通常远小于表面耗尽区的宽度.

半导体表面 半导体表面 半导体表面 E E E C C C E E E g g g E E E y y y q q q i i i y y y q q q y y y q q q B B B S S S E E E F F F y y y > > > ( ( ( 0 0 0 ) ) ) S S S E E E V V V 半导体 半导体 半导体 氧化层 氧化层 氧化层 x x x i i i MOS二极管 一、表面耗尽区:下图为p型半导体表面更为详细的能带图.在半导体衬底内的静电势Ψ定义为零.在半导体表面Ψ= Ψs,Ψs称为表面电势.将电子与空穴的浓度表示为Ψ的函数: 其中当能带如图向下弯曲时,Ψ为正值.表面载流子密度为

半导体表面 半导体表面 半导体表面 E E E C C C E E E g g g E E E y y y q q q i i i y y y q q q y y y q q q B B B S S S E E E F F F y y y > > > ( ( ( 0 0 0 ) ) ) S S S E E E V V V 半导体 半导体 半导体 氧化层 氧化层 氧化层 x x x i i i MOS二极管 根据以上的讨论,以下各区间的表面电势可以区分为 Ψs<0:空穴积累(能带向上弯曲); Ψs =0:平带情况; ΨB>Ψs>0:空穴耗尽(能带向下弯曲); Ψs=ΨB:禁带中心,即ns=np=ni(本征浓度); Ψs>ΨB:反型(能带向下弯曲超过费米能级). 电势为距离的函数,可由一维的泊松方程式求得为 其中ρs(x)为位于x处的单位体积电荷密度,而εs为介电常数

半导体表面 半导体表面 半导体表面 E E E C C C E E E g g g E E E y y y q q q i i i y y y q q q y y y q q q B B B S S S E E E F F F y y y > > > ( ( ( 0 0 0 ) ) ) S S S E E E V V V 半导体 半导体 半导体 氧化层 氧化层 氧化层 x x x i i i MOS二极管 下面采用耗尽近似法分析p-n结.当半导体耗尽区宽度达到W时,半导体内的电荷为ρs=-qNAW,积分泊松方程式可得距离x的函数的表面耗尽区的静电势分布: 表面电势Ψs为 注意此电势分布与单边的n+-p结相同。 当Ψs大于ΨB时表面即发生反型,然而,我们需要一个准则来表示强反型的起始点.超过该点表示此时反型层中的电荷数已相当显著.

半导体表面 半导体表面 半导体表面 E E E C C C E E E g g g E E E y y y q q q i i i y y y q q q y y y q q q B B B S S S E E E F F F y y y > > > ( ( ( 0 0 0 ) ) ) S S S E E E V V V 半导体 半导体 半导体 氧化层 氧化层 氧化层 x x x i i i MOS二极管 设定表面电荷等于衬底杂质浓度是一个简单的准则,即ns=NA.因为,由式 可得 上式表示需要一电势ΨB将表面的能带弯曲至本征的条件(Ei=EF),接着还需要一额外的电势ΨB,以将表面的能带弯曲至强反型的状态. 当表面为强反型时,表面的耗尽区宽度达到最大值.因此,当Ψs等于Ψs(inv)时,可得到表面耗尽区的最大宽度Wm

7 10 m m / 1 m W 度 GaAs 宽 Si 区 尽 耗 0 . 1 大 最 0 . 01 14 15 16 17 18 10 10 10 10 10 - 3 N / cm 杂质浓度 B MOS二极管 或 和 硅和砷化镓中Wm与杂质浓度的关系如图,且p型半导体中NB等于NA,n型半导体中NB等于ND。 例1:一NA=1017cm-3的理想金属-二氧化硅-硅二极管,试计算表面耗尽区的最大宽度. 解:室温下kT/q=0.026V,且ni=9.65×109cm-3,Si的介电常数为11.9×8.85×10-14F/cm,由式可得

MOS二极管 二、理想MOS曲线 图(a)为一理想MOS二极管的能带图,电荷的分布情形如图(b)所示.在没有任何功函数差时,外加的电压部分降落在氧化层,部分降落在半导体,因此 其中V0为降落在氧化层的电压,且由图(c)可得 其中E0为氧化层中的电场,Qs为半导体中每单位面积的电荷量,而C0=εox/d为每单位面积的氧化层电容.其相对应的静电势分布如图(d)所示.

MOS二极管 MOS二极管的总电容C是由氧化层电容C0与半导体中的势垒电容Cj相互串联而成,如图。 其中Cj=εs/W,如同突变p-n结一样. 由上式和 可以消去W而得到电容的公式为

MOS二极管 由 可见,当表面开始耗尽时,电容值将会随着金属平行板上的电压增加而下降.当外加电压为负时,无耗尽区产生,将在半导体表面得到积累的空穴,因此,全部的电容值将很接近氧化层电容εox/d. 反之,当强反型发生时,即使增加所施加的电压也无法增加耗尽区的宽度,表面电势达到Ψs(inv),且注意每单位面积的电荷为qNAWm,可得在强反型刚发生时的金属平行板电压,称为阈值电压:

MOS二极管 一旦当强反型发生时,势垒电容保持Cj=εs/Wm的最小值,总电容将 一理想MOS二极管的典型电容-电压特性如图所示,包含耗尽近似与精确值(实线).值得注意的是,耗尽近似与精确值相当接近. 对n型衬底而言,所有的考虑,在经过变更相对应符号与标志后(如将Qp换成Qn),也同样有效.其电容-电压特性亦有相同的外观,不过彼此将成镜面对称,且对于一n型衬底的理想MOS二极管而言,其阈值电压将为负值.

MOS二极管 在前一图中,我们假设当金属平行板上的电压发生变化时,所有增加的电荷将出现在耗尽区的边缘,事实上,只有当测量频率相当高对才会发生. 然而,假如当测量频率足够低时,使得表面耗尽区内的产生-复合率与电压变化率相当或是更快时,电子浓度(少数载流子)与反型层中的电荷可以跟随交流的信号.因此导致强反型时的电容只有氧化层电容C0而已.右图为在不同频率下所测得的MOS的C-V曲线,注意低频的曲线发生在≤100Hz时.

MOS二极管 例2:一理想MOS二极管的NA=1017cm-3且d=5nm,试计算其C-V曲线中的最小电容值.SiO2的相对介电常数为3.9。 解: 在VT时的最小电容Cmin 因此Cmin约为C0的13%

MOS二极管 SiO2-Si MOS二极管 对所有的MOS二极管而言,金属-SiO2-Si为最受广泛研究.SiO2-Si系统的电特性近似于理想的MOS二极管.然而,对于广泛使用的金属电极而言,其功函数差一般不为零,而且在氧化层内部或SiO2-Si界面处存在的不同电荷,将以各种方式影响理想MOS的特性. 一、功函数差 对于一有固定功函数qm的特定金属,它与功函数为qs的半导体的功函数差qms=q(m-s)将会随着半导体的掺杂浓度而改变.如图。随着电极材料与硅衬底掺杂浓度的不同,qms可能会有超过2V的变化。

MOS二极管 考虑一在独立金属与独立半导体间的氧化层夹心结构,如图(a)。在此独立的状态下,所有的能带均保持水平,即平带状况.当三者结合在一起,在热平衡状态下,费米能级必为定值,且真空能级必为连续,为调节功函数差,半导体能带需向下弯曲,如图(b). 因此在热平衡状态下,金属含正电荷,而半导体表面则为负电荷.为达到理想平带状况,需外加一相当于功函数差qms的电压,此对应至图(a)的状况,在此需在金属外加一负电压VFB=ms,此电压称为平带电压.

金属 金属 + + 可动离子电荷 可动离子电荷 N N a a 氧化层陷阱 氧化层陷阱 + + K K ( ( Q Q ) ) Q Q ( ( ) ) 电荷 电荷 m m ot ot + + + + + + SiO SiO 2 2 ( ( Q Q ) ) 氧化层固定电荷 氧化层固定电荷 - - - - - - f f + + + + + + + + + + + + ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ Q Q ( ( ) ) 界面陷阱电荷 界面陷阱电荷 it it Si Si MOS二极管 二、界面陷阱与氧化层电荷: MOS二极管还受氧化层内的电荷以及SiO2-Si界面陷阱的影响.这些基本的陷阱与电荷的类型如图所示,包括有界面陷阱电荷、氧化层固定电荷(fixed oxide charge)、氧化层陷阱电荷以及可动离子电荷.

金属 金属 + + 可动离子电荷 可动离子电荷 N N a a 氧化层陷阱 氧化层陷阱 + + K K ( ( Q Q ) ) Q Q ( ( ) ) 电荷 电荷 m m ot ot + + + + + + SiO SiO 2 2 ( ( Q Q ) ) 氧化层固定电荷 氧化层固定电荷 - - - - - - f f + + + + + + + + + + + + ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ Q Q ( ( ) ) 界面陷阱电荷 界面陷阱电荷 it it Si Si MOS二极管 界面陷阱电荷Qit是由SiO2-Si界面特性所造成,且与界面处的化学键有关.这些陷阱位于SiO2-Si界面处,而其能量则位于硅的禁带中。这些界面陷阱密度(即每单位面积与单位电子阴的界面陷阱数目)与晶体方向有关.在<100>方向,其界面陷阱密度约比<111>方向少一个数量级. 目前在硅基上采用热氧化生成二氧化硅的MOS二极管中所产生的大部分界面陷阱,可用低温450℃的氢退火加以钝化.在<100>方向的Qit/q值可以小于1010cm-2,大约为每105个表面原子会存在一个界面陷阱电荷.在<111>方向的硅衬底中,Qit/q约为1011cm-2.

金属 金属 + + 可动离子电荷 可动离子电荷 N N a a 氧化层陷阱 氧化层陷阱 + + K K ( ( Q Q ) ) Q Q ( ( ) ) 电荷 电荷 m m ot ot + + + + + + SiO SiO 2 2 ( ( Q Q ) ) 氧化层固定电荷 氧化层固定电荷 - - - - - - f f + + + + + + + + + + + + ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ Q Q ( ( ) ) 界面陷阱电荷 界面陷阱电荷 it it Si Si MOS二极管 氧化层固定电荷Qf位于距离SiO2-Si界面约3nm处.此电荷固定不动,且即使表面电势有大范围的变化仍不会有充放电现象发生.一般来说,Qf为正值,且与氧化、退火的条件以及硅的晶体方向有关.一般认为当氧化停止时,一些离子化的硅留在界面处,而这些离子与表面未完全成键的硅结合(如Si-Si或Si-O键),可能导致正的界面电荷Qf产生. Qf可视为是SiO2-Si界面处的片电荷层.对小心呵护处理的SiO2-Si界面系统而言,其氧化层固定电荷量在<100>方向表面约为1010cm-2,而在<111>方向表面约为5×1010cm-2.由于<100>方向具有较低的Qit与Qf,所以常用<100>硅基MOSFET.

金属 金属 + + 可动离子电荷 可动离子电荷 N N a a 氧化层陷阱 氧化层陷阱 + + K K ( ( Q Q ) ) Q Q ( ( ) ) 电荷 电荷 m m ot ot + + + + + + SiO SiO 2 2 ( ( Q Q ) ) 氧化层固定电荷 氧化层固定电荷 - - - - - - f f + + + + + + + + + + + + ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ ´ Q Q ( ( ) ) 界面陷阱电荷 界面陷阱电荷 it it Si Si MOS二极管 氧化层陷阱电荷Qot常随着二氧化硅的缺陷产生,这些电荷可由如X光辐射或是高能量电子轰击而产生.这些陷阱分布于氧化层内部,大部分与工艺有关的Qot可以低温退火加以去除. 钠或其他碱金属离子的可动离子电荷Qm,在高温(如大于100℃)或强电场的工作条件下,可在氧化层内移动. 在高偏压及高温的工作环境下,由碱金属离子所造成的污染,可能会引发半导体器件稳定度的问题.在这些情况之下,可动离子电荷可以在氧化层内来回地移动,并使得C-V曲线沿着电压轴产生位移.因此,在器件制作的过程中需特别注意以消除可动离子电荷.

MOS二极管 下面将估算上述电荷对平带电压所产生的影响.考虑如图中位于每单位面积氧化层内固定电荷的正片电荷Qo,如图上半部所示,这些正的片电荷将在金属与半导体内感应一些负电荷.对泊松方程式做一次积分,可以得到电场的分布情形,如图下半部所示.此处我们假设没有功函数差,即qms=0。

MOS二极管 为达到平带状态(即半导体内无感应电荷),必须在金属上施加一负电压,如图所示.当负电压增加时,金属获得更多的负电荷,因此电场向下偏移,直到半导体表面的电场为零.在此条件之下,电场分布的面积即为平带电压VFB: 因此,平带电压与片电荷密度Qo及其在氧化层中的位置xo有关.当片电荷非常靠近金属时,即xo=0,则将无法在硅基中感应电荷,且不会对平带电压造成影响。反之,当片电荷非常靠近半导体时,即xo=d,就如同氧化层固定电荷一般,将具有最大的影响力,并将平带电压提升为

MOS二极管 对一般任意分布于氧化层中的空间电荷而言,平带电压可表示为 其中ρ(x)为氧化层中的体电荷密度.倘若知道氧化层陷阱电荷的体电荷密度ρot(x) ,以及可动离子电荷的体电荷密度ρm(x) ,就可以得到Qot与Qm以及它们对于平带电压的贡献: 假使功函数差qms的值不为零,且若界面陷阱电荷的值可以忽略不计,由实验测得的电容-电压曲线将会从理想的理论曲线平移一个数值,

1 1 . . 0 0 ( ( c c ) ) ( ( b b ) ) ( ( a a ) ) 0 0 C C / / C C 0 0 . . 5 5 0 0 - - V V 0 0 + + V V C - V MOS二极管 图中(a)为一理想MOS二极管的C-V特性.由于受非零值的qms、Qf、Qm与Qot的影响,C-V曲线将平行偏移.平移的C-V曲线如图中(b)所示.此外若存有大量的界面陷阱电荷,这些位于界面陷阱处的电荷将随表面电势而变,C-V曲线会随其表面电势的变化而改变,因此由于界面陷阱电荷, C-V曲线变为图中(c)所示, C-V曲线不但会扭曲变形,而且会产生偏移.

MOS二极管 例3:试计算一NA=1017cm-3及d=5nm的n+多晶硅-SiO2-Si二极管的平带电压.假设Qt与Qm在氧化层中可被忽略,且Qf/q为5×l011cm-2. 解:由图可知,在NA=1017cm-3时,对n+多晶硅系统而言,其ms为-0.98eV,且 所以

MOS二极管 例4:假设在氧化层中的氧化层陷阱电荷Qot的单位体积电荷密度ρot(y)为一个三角形分布,此分布情形可用(1018-5×1023×x)cm-3函数加以描述,其中x为所在位置与金属-氧化层界面间的距离.氧化层厚度为20nm.试计算因Qot所造成的平带电压的变化量. 解:由 和 得到

MOS二极管 电荷耦合器件 (CCD) 电荷耦合器件的结构如图所示,其器件是由覆盖于半导体衬底上的连续绝缘层(氧化层)上的紧密排列的MOS二极管阵列所组成.CCD可以实现包含影像感测以及信号处理等广泛的电子功能.CCD的工作原理牵涉到电荷储存以及由栅极电压控制的输运行为.图中显示对CCD施加一足够大的正偏压脉冲于所有的电极之上,以使其表面发生耗尽. 一较高的偏压施加于中央的电极上,使中央的MOS结构有较深的耗尽区,并形成一电势阱.亦即由于中央电极下方较深的耗尽层而产生一个中央呈深阶状的电势分布.此时所感应生成的少数载流子(电子),则会被收集至这个电势阱中。

f f f f = = = = f f f f = = = = f f f f = = = = 5 5 5 5 V V V V 10 10 10 10 V V V V 5 5 5 5 V V V V 1 1 1 1 2 2 2 2 3 3 3 3 SiO SiO SiO SiO 2 2 2 2 - - - - p p p p Si Si Si Si f f f ( ( ( a a a ) ) ) 高压加于 高压加于 高压加于 2 2 2 f f f f = = = = f f f f = = = = f f f f = = = = 5 5 5 5 V V V V 10 10 10 10 V V V V 15 15 15 15 V V V V 1 1 1 1 2 2 2 2 3 3 3 3 SiO SiO SiO SiO 2 2 2 2 - - - - p p p p Si Si Si Si f f f b b b ( ( ( ) ) ) 加更高电压,以使电荷 加更高电压,以使电荷 加更高电压,以使电荷 输运 输运 输运 3 3 3 MOS二极管 电荷耦合器件 (CCD) 假使右侧电极上的电压增加到超过中央电极的电压时,我们可以得到如图(b)所示的电势分布。在此情况之下,少数载流子将由中央电极转移至右侧电极。随后,电极的电势可重新调整,使得静止的储存状态位于右侧的电极.由这一连串连续的过程,我们可以成功地沿着一线性阵列传送载流子.

源极 源极 栅极 栅极 漏极 漏极 Z Z d d SiO SiO 2 2 + + n n r r j j + + n n L L p p z z z y y y ( ( ( E E E ) ) ) y y y x x x ( ( ( E E E ) ) ) x x x 衬底 衬底 衬底 MOSFET基本原理 MOSFET有许多种缩写形式,如IGFET、MISFET、MOST等.n沟道MOSFET的透视图如图所示.它是一个四端点器件,由一个有两个n+区域(即源极与漏极)的p型半导体所组成. 氧化层上方的金属称为栅极(gate),高掺杂或结合金属硅化物的多晶硅可作为栅极电极,第四个端点为一连接至衬底的欧姆接触.基本的器件参数有沟道长度L(为两个n+-p冶金结之间的距离)、沟道宽度Z、氧化层厚度d、结深度rj以及衬底掺杂浓度NA. 器件中央部分即为MOS二极管.

源极 源极 栅极 栅极 漏极 漏极 Z Z d d SiO SiO 2 2 + + n n r r j j + + n n L L p p z z z y y y ( ( ( E E E ) ) ) y y y x x x ( ( ( E E E ) ) ) x x x 衬底 衬底 衬底 MOSFET基本原理 MOSFET的基本特性 MOSFET中源极接点作为电压的参考点.当栅极无外加偏压时,源极到漏极电极之间可视为两个背对背相接的p-n结,而由源极流向漏极的电流只有反向漏电流. 当外加一足够大的正电压于栅极上时,MOS结构将被反型,以致于在两个n+型区域之间形成表面反型层即沟道.源极与漏极通过这一导电的表面n型沟道相互连结,并可允许大电流流过.沟道的电导可通过栅极电压的变化来加以调节.衬底接点可连接至参考电压或相对于源极的反向偏压,衬底偏压亦会影响沟道电导.

MOSFET基本原理 一、输出特性: 当在栅极上施加一偏压,并在半导体表面产生反型.若在漏极加一小量电压,电子将会由源极经沟道流向漏极(对应电流为由漏极流向源极).因此,沟道的作用就如同电阻一般,漏极电流ID与漏极电压成比例,此即如图(a)右侧恒定电阻直线所示的线性区.

MOSFET基本原理 半导体表面强反型形成导电沟道时,沟道呈现电阻特性,当漏-源电流通过沟道电阻时将在其上产生电压降。若忽略其它电阻,则漏端相当于源端的沟道电压降就等于漏-源偏置电压VDS。由于沟道上存在电压降,使栅绝缘层上的有效电压降从源端到漏端逐渐减小,降落在栅下各处绝缘层上的电压不相等,反型层厚度不相等,因而导电沟道中各处的电子浓度不相等。当漏极电压持续增加,直到漏端绝缘层上的有效电压降低于表面强反型所需的阈值电压VT时,在靠近y=L处的反型层厚度xi将趋近于零,此处称为夹断点P,如图(b). 此时的漏-源电压称为饱和电压VDsat。超过夹断点后,漏极的电流量基本上维持不变,因为当VD>VDsat时,在P点的电压VDsat保持固定.

MOSFET基本原理 沟道被夹断后,若VG不变,则当漏极电压持续增加时,超过夹断点电压VDsat的那部分即VDS-VDsat将降落在漏端附近的夹断区上,因而夹断区将随VDS的增大而展宽,夹断点P随之向源端移动,但由于P点的电压保持为VDsat不变,反型层内电场增强而同时反型载流子数减少,二者共同作用的结果是单位时间流到P点的载流子数即电流不变。一旦载流子漂移到P点,将立即被夹断区的强电场扫入漏区,形成漏源电流,而且该电流不随VDS的增大而变化,即达到饱和。此即为饱和区,如图(c)所示.当然,如果VDS过大,漏端p-n结会发生反向击传。

MOSFET基本原理 为推导出基本的MOSFET特性,将基于下列的理想条件: (1)栅极结构如理想MOS二极管,即无界面陷阱、固定氧化层电荷或功函数差; (2)仅考虑漂移电流; (3)反型层中载流子的迁移率为固定值; (4)沟道内杂质浓度为均匀分布; (5)反向漏电流可忽略; (6)沟道中由栅极电压所产生的垂直于ID电流方向的电场远大于由漏极电压所产生的平行于ID电流方向的电场. 最后的一个条件称为缓变沟道近似法,通常可适用于长沟道的MOSFET中,基于此种近似法,衬底表面耗尽区中所包含的电荷量仅由栅极电压产生的电场感应所生成.

MOSFET基本原理 图(a)为工作于线性区的MOSFET.根据上述的理想条件,如图(b)所示,在半导体中距离源极长度为y处的每单位面积所感应的电荷,其为图(a)中间的放大部分,由式 和 可得 其中Ψs(y)为位于y处的表面电势,而Co=εox/d为每单位面积的栅极电容.

MOSFET基本原理 由于QS为反型层中每单阿位面积电荷量Qn与表面耗尽区中每单位面积的电荷量QSC的总和,所以我们可以得到 反型层的表面电势Ψs(y)可以近似为2ΨB+V(y),其中V(y)为y点与源极电极(可视为接地)间的反向偏压,如图(c)所示.表面耗尽区内的电荷Qsc(y)如前所述可表示为 将上式代入前式可得

MOSFET基本原理 沟道中在y处的电导率可近似为 对一固定的迁移率而言,沟道电导可表示为 积分项为反型层中单位面积中的总电荷量,即 所以 每一基本片段dy(如图(b))的沟道电阻为

MOSFET基本原理 此基本片段上的电压降为 其中ID为与y无关的漏极电流.将式 代入上式,并由源极(y=0,V=0)积分至漏极(y=L,V=VD)可得

MOSFET基本原理 下图为根据上式所得到的理想MOSFET的电流-电压特性曲线.对一已知的VG而言,漏极电流一开始会随漏极电压线性增加(线性区),然后逐渐水平,最后达到一饱和值(饱和区).虚线指出当电流达到最大值时的漏极电压( 即VDsat )的轨迹. 当VD很小时,式 可简化为

MOSFET基本原理 其中 为阈值电压,画出ID对VG的曲线(对一已知的小VD而言),此曲线称为转移特性曲线,阈值电压可以由对VG轴线性外插得出.在线性区,沟道电导gD以及跨导gm可表示为 当漏极电压增加至使得反型层中的电荷值Qn(y)在y=L处为零时,在漏极处的移动电子数目将大幅地减少,此点称为夹断点.其漏极电压与漏极电流可表示为VDsat和IDsat.

MOSFET基本原理 当漏极电压大于VDsat时,则达到饱和区.在Qn(L)=0的条件下,由式 得到VDsat的值为 将上式代入式

MOSFET基本原理 可得饱和电流为 对低衬底掺杂与薄氧化层而言,饱和区的阈值电压VT与式 相同.在高掺杂浓度下,VT变得与VG有关. 对一处于饱和区的理想MOSFET而言,沟道电导为零,且跨导由最上面式子得到:

MOSFET基本原理 例5:对一n型沟道n型多晶硅-SiO2-Si的MOSFET,其栅极氧化层厚8nm,NA=1017cm-3且VG=3V,试计算其VDsat。 解: 所以

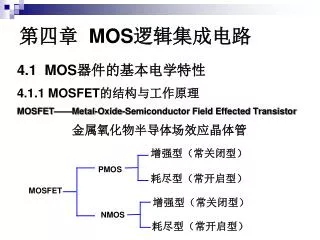

MOSFET基本原理 MOSFET的种类 依据反型层的形式,MOSFET有四种基本的形式.假如在零栅极偏压下,沟道的电导非常低,必须在栅极外加一正电压以形成n沟道,则此器件为增强型(或称常关型)n沟道MOSFET.如果在零偏压下,已有n沟道存在,而必须外加一负电压来排除沟道中的载流子,以降低沟道电导,则此器件为耗尽型(或称常开型)n沟道MOSFET.同样也有p沟道增强型与耗尽型MOSFET. 需注意的是,对增强型n沟道器件而言,必须施加一个大于阈值电压VT的正栅极偏压,才能有显著的漏极电流流通.对耗尽型n沟道器件而言,在VG=0时已有大量电流流通,且变动栅极电压可以增减其电流.以上的讨论在改变极性后,亦可适用于p沟道器件.

类型 类型 剖面图 剖面图 输出特性 输出特性 转移特性 转移特性 + + + = = = + + + V V V G G G 4 4 4 V V V I I I I I I G G G D D D D D D I I I D D D D D D 3 3 3 n n 沟增强型 沟增强型 ( ( ) ) 常闭 常闭 2 2 2 1 1 1 + + + + + + p p p n n n n n n V V V - - - + + + V V V 0 0 0 0 0 0 D D D Tn Tn Tn + + + + + + G G G = = = V V V 1 1 1 V V V - - - I I I I I I I I I G G G D D D D D D D D D D D D 0 0 0 n n 沟耗尽型 沟耗尽型 V V V ( ( ) ) - - - 常开 常开 1 1 1 Tn Tn Tn + + + + + + + + + - - - - - - p p p 2 2 2 n n n n n n 0 0 0 V V V 0 0 0 D D D V V V n n 沟道 沟道 G G G - - - V V V - - - G G G - - - 0 0 0 G G G V V V V V V D D D I I I + + + - - - - - - Tp Tp Tp D D D 1 1 1 0 0 0 D D D - - - p p 沟增强型 沟增强型 2 2 2 ( ( ) ) 常闭 常闭 - - - 3 3 3 + + + + + + p p p p p p n n n = = = - - - V V V 4 4 4 V V V I I I I I I G G G D D D D D D + + + + - - - - G G G G - - - - V V V I I I I - - - 0 0 0 G G G V V V D D D D D D D D D D D - - - + + + 1 1 1 0 0 0 2 2 2 p p 沟耗尽型 沟耗尽型 ( ( ) ) 常开 常开 0 0 0 + + + + + + + + p p p p p p p p n n n n I I I = = = - - - V V V 1 1 1 V V V I I I D D D p p p 沟道 沟道 沟道 G G G D D D MOSFET基本原理

MOSFET基本原理 阈值电压控制 阈值电压是MOSFET最重要的参数之一,理想的阈值电压如式 然而,当考虑固定氧化层电荷以及功函数差时,将会有一平带电压偏移.除此之外,衬底偏压同样也能影响阈值电压.当一反向偏压施加于衬底与源极之间时,耗尽区将会加宽,欲达到反型所需的阈值电压必须增大,以提供更大的Qsc。可改变阈值电压的各项参数如下: 其中VBS为反向衬底-源极偏压 。